digital

# NIA20 Technical Reference Manual

EK-NIA20-RM-001

# NIA20 Technical Reference Manual

•

Prepared by Educational Services of Digital Equipment Corporation

1st Edition, January 1985

© Digital Equipment Corporation 1985.

#### All Rights Reserved.

#### Printed in U.S.A.

The material in this manual is for informational purposes and is subject to change without notice.

Digital Equipment Corporation assumes no responsibility for any errors that may appear in this manual.

This book was produced on a DIGITAL Word Processing System. Book production was done by Educational Services Development and Publishing in Marlboro, MA.

The following are trademarks of Digital Equipment Corporation:

| digilal <sup>™</sup> | MICRO/PDP-11 | RSX            |

|----------------------|--------------|----------------|

| DEC                  | MicroVAX     | RT             |

| DECmate              | PDP          | UNIBUS         |

| DECUS                | P/OS         | VAX            |

| DECwriter            | Professional | VAXcluster     |

| DIBOL                | Q-Bus        | VMS            |

| LSI-11               | Rainbow      | VT             |

| MASSBUS              | RSTS         | Work Processor |

## CONTENTS

•

Page

PREFACE

CHAPTER 1 INTRODUCTION

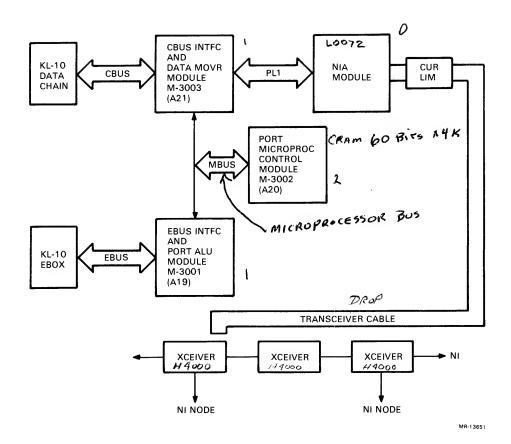

| 1.1            | NIA20 SUBSYSTEM OVERVIEW1-3                      |

|----------------|--------------------------------------------------|

| 1.1.1          | Network Interconnect Adapter Module1-4           |

| 1.1.2          | Port                                             |

| 1.1.2.1        | EBus Interface/Port ALU Module (M3001)1-5        |

| 1.1.2.2        | Port Microprocessor Control Module (M3002)1-6    |

| 1.1.2.3        | CBus-PLI Interface Module (M3003)1-6             |

| 1.1.3          | H4000 Transceiver                                |

| 1.1.3.1        | Transmit Function                                |

| 1.1.3.2        | Watchdog Timer Function1-7                       |

| 1.1.3.3        | Collision Presence Function                      |

| 1.1.3.4        | Collision Presence Test Function (Heartbeat) 1-7 |

| 1.1.3.5        | Receive Function                                 |

| 1.1.3.6        | DC To DC Converter1-7                            |

| 1.1.3.7        | Coaxial Cable Connection                         |

| 1.1.3.8        | Transceiver Cable Connections                    |

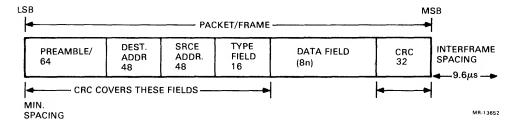

| 1.2            | ETHERNET SPECIFICATION OVERVIEW                  |

| 1.2.1          | Packet Format                                    |

| 1.2.1.1        | Maximum Packet Size                              |

| 1.2.1.2        | Minimum Packet Size                              |

| 1.2.1.3        | Preamble                                         |

| 1.2.1.4        | Destination Address                              |

| 1.2.1.5        | Source Address1-10                               |

| 1.2.1.6        | Type Field                                       |

| 1.2.1.7        | Data Field1-10                                   |

| 1.2.1.8        | Packet Check Sequence                            |

| 1.2.1.9        | Round-Trip Delay1-10                             |

| 1.2.2          | Control Procedures1-10                           |

| 1.2.2.1        | Defer1-10                                        |

| 1.2.2.2        | Transmit1-11                                     |

| 1.2.2.3        | Abort1-11                                        |

| 1.2.2.4        | Retransmitl-11                                   |

| 1.2.2.5        | Backoff                                          |

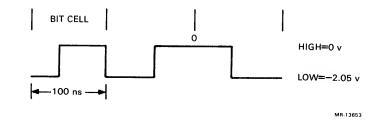

| 1.2.3<br>1.2.4 | Manchester Encoding                              |

| 1.2.4          | Carrier Sense                                    |

| 1.2.6          | Transceiver Connections                          |

| 1.2.0          | Transceivers1-12                                 |

1.0.1

### CHAPTER 2 IMPLEMENTATION

| 2.1      | IMPLEMENTATION OVERVIEW                                      |

|----------|--------------------------------------------------------------|

| 2.2      | QUEUE STRUCTURE                                              |

| 2.2.1    | Queue Linkage2-2                                             |

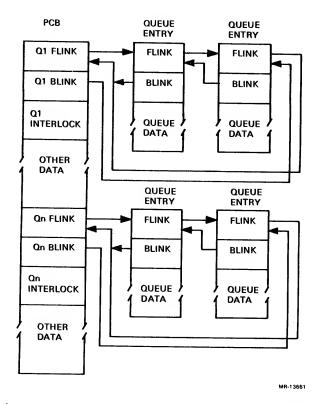

| 2.2.2    | Queue Interlocks2-3                                          |

| 2.2.3    | Queue Locations                                              |

| 2.3      | QUEUE HANDLING                                               |

| 2.3.1    | Queue Headers                                                |

| 2.3.2    | Entry Linking                                                |

| 2.3.3    | Entry Removal                                                |

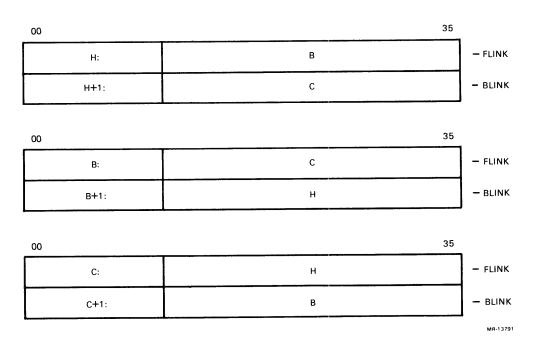

| 2.3.3.1  | Buffer Segment Descriptors                                   |

| 2.3.3.2  |                                                              |

| 2.3.3.2  | Buffer Segment Descriptor Format                             |

| 2.4.1    | COMMANDS AND RESPONSES                                       |

|          | Command and Response Formats                                 |

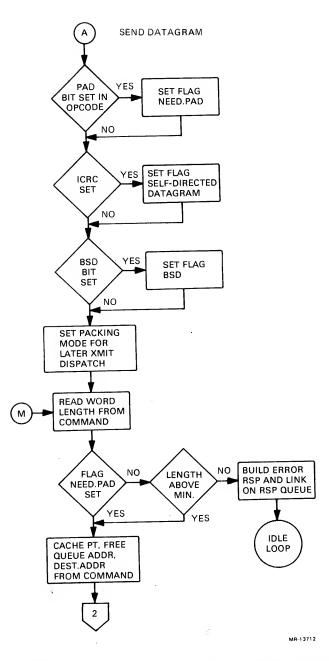

| 2.4.1.1  | Send Datagram (SNDDG) Command                                |

| 2.4.1.2  | Datagram Sent (DGSNT) Response                               |

| 2.4.1.3  | Datagram Received (DGRCV) Response                           |

| 2.4.1.4  | Load Protocol Type Table (LDPTT) Command2-24                 |

| 2.4.1.5  | Protocol Type Table Loaded (PTTLD) Response2-25              |

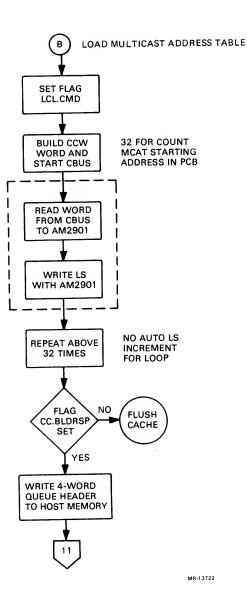

| 2.4.1.6  | Load Multicast Address Table (LDMCAT)                        |

|          | Command2-25                                                  |

| 2.4.1.7  | MCAT Loaded Response LDMCAT                                  |

| 2.4.1.8  | Read and Clear Performance Counters RCCNT                    |

|          | Command                                                      |

| 2.4.1.9  | Counters Read or Cleared (CNTRC) Response2-27                |

| 2.4.1.10 | Write Port Link Interface (WRTPLI) Command2-32               |

| 2.4.1.11 | Port Link Interface Written (PLIWRT)                         |

|          | Response                                                     |

| 2.4.1.12 | Read Port Link Interface (RDPLI) Command2-33                 |

| 2.4.1.13 | Port Link Interface Read (PLIRD) Response2-34                |

| 2.4.1.14 | Read NI Station Address (RDNSA) Command2-35                  |

| 2.4.1.15 | NI Station Address Read (NSARD) Response2-36                 |

| 2.4.1.16 | Write NI Station Address (WRTNSA) Command2-37                |

| 2.4.1.17 | NI Station Address Written (NSAWRT) Response2-38             |

| 2.4.2    | Self-Directed Commands Loopback                              |

| 2.5      | DATA FORMATTING/PACKING MODE                                 |

| 2.6      | MAINTENANCE OPERATION PROTOCOL                               |

| 2.7      | ERROR HANDLING                                               |

| 2.7.1    | Error Events                                                 |

| 2.7.2    | Discarded Datagrams2-41                                      |

| 2.7.3    | Event Counters                                               |

| 2.8      | CONTROL AND STATUS REGISTER                                  |

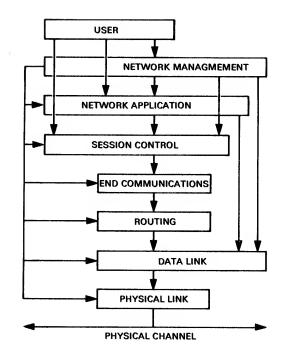

| 2.9      | NETWORK ARCHITECTURE AND FUNCTIONAL LAYERS2-43               |

| 2.9.1    | Physical Link Layer and Data Link Layers2-43                 |

| 2.9.2    | Routing Layer                                                |

| 2.9.3    | End-to-End Communications Layer                              |

|          | Line to fine communications hayer to the terrest of the 14 . |

.

| 2.9.4<br>2.9.5<br>2.9.6<br>2.9.7<br>2.9.8<br>2.9.9                                                                                                                       | Session Control Layer                                                                                                                                                                                                                                                                                                                                                                                                            |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CHAPTER 3                                                                                                                                                                | INSTALLATION OF NIA20 IN KL10-E                                                                                                                                                                                                                                                                                                                                                                                                  |

| 3.1<br>3.2<br>3.3<br>3.4<br>3.4.1<br>3.4.2<br>3.4.3<br>3.4.4<br>3.4.5<br>3.4.5<br>3.4.5.1<br>3.4.5.2<br>3.4.6<br>3.4.7                                                   | OVERVIEW.3-1UNPACKING AND CHECKOUT.3-7EQUIPMENT NEEDED FOR INSTALLATION AND CHECKOUT.3-7INSTALLATION PROCEDURE.3-8Preinstallation Checkout.3-8Backplane Wire Adds.3-8Installation of Port Modules.3-9Power Supply Regulator Installation.3-12Installation of NIA20 Card Cage/Internal Cable.3-13Installation of NIA20 Current Limiter.3-17Harness Installation.3-17Installation of KL10 Adapter Board and Blank3-23Checkout.3-24 |

| CHAPTER 4                                                                                                                                                                | FUNCTIONAL DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                           |

| 4.1<br>4.1.1<br>4.1.2<br>4.1.3<br>4.2<br>4.3<br>4.3.1<br>4.3.2<br>4.4<br>4.5<br>4.5.1<br>4.5.2<br>4.5.3<br>4.5.3<br>4.5.4<br>4.5.5<br>4.5.5<br>4.5.6<br>4.5.7<br>4.5.7.1 | PORT STATES.4-1Uninitialized.4-1Disabled.4-1Enabled.4-1CONTROL AND STATUS REGISTER.4-2EBUS.4-6EBus Interrupts.4-10Examine/Deposit Request Response.4-12CBUS.4-13PLI.4-20PLI Interface Signals.4-21Data (7:0) (Asserted High).4-21Select (Asserted Low).4-21Receiver Attention (Asserted High).4-22Transmitter Attention (Asserted High).4-22PLI/Link Control (Asserted High).4-22                                                |

| 4.5.7.5                                                                                                                                                                                                         | Read Receiver Status Register                                  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| 4.5.7.6                                                                                                                                                                                                         | (RD REC STATUS)4-24<br>Read Receive Memory Used Buffer Address |

| 4.5.7.0                                                                                                                                                                                                         | List (RD USED BUF LST)                                         |

| 4.5.7.7                                                                                                                                                                                                         | Transfer Byte from Receive Memory to the                       |

|                                                                                                                                                                                                                 | Transmit Buffer (REC TO XMIT BUF)                              |

| 4.5.7.8                                                                                                                                                                                                         | Reset Receive Attention (RESET REC ATT) 4-24                   |

| 4.5.7.9                                                                                                                                                                                                         | Enable Link Control/Disable Link Control4-24                   |

| 4.5.7.10                                                                                                                                                                                                        | Write Receive Memory Buffer Read Address                       |

|                                                                                                                                                                                                                 | to the Read Memory Address Register                            |

|                                                                                                                                                                                                                 | (WT REC BUF RD ADRS REGISTER)                                  |

| 4.5.7.11                                                                                                                                                                                                        | Write Free Buffer List (WT FREE BUF LST)4-25                   |

| 4.5.7.12                                                                                                                                                                                                        | Clear Receive Buffer (CLR RCV BUF)                             |

| 4.5.7.13                                                                                                                                                                                                        | Write Address Register (WT ADRS REG)4-25                       |

| 4.5.7.14                                                                                                                                                                                                        | Read Register (RD REG)                                         |

| 4.5.7.15                                                                                                                                                                                                        | Write Register (WT REG)                                        |

| 4.5.8                                                                                                                                                                                                           | Transmit Parity (Odd) (TTL Asserted High)4-25                  |

| 4.5.9<br>4.5.10                                                                                                                                                                                                 | Receive Data Parity (Odd) (TTL Asserted High)4-25              |

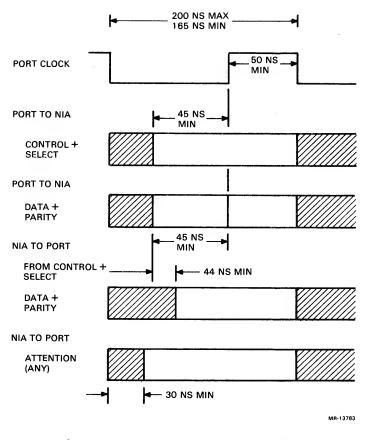

| 4.5.10                                                                                                                                                                                                          | Clock Timing (PLI Bus)                                         |

| 4.5.12                                                                                                                                                                                                          | Receive and Transmit Status                                    |

| 4.6                                                                                                                                                                                                             | SIMPLIFIED NIA BLOCK DESCRIPTION                               |

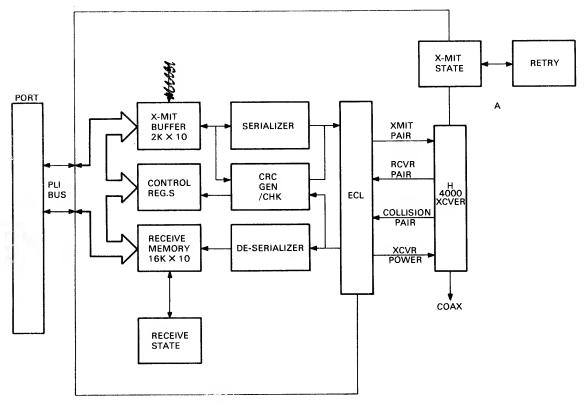

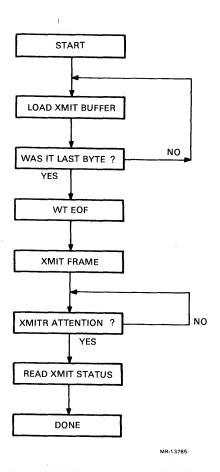

| 4.6.1                                                                                                                                                                                                           | Simplified Transmit Operation,                                 |

| -                                                                                                                                                                                                               |                                                                |

| 4.6.2                                                                                                                                                                                                           | Simplified Receive Operation                                   |

| 4.6.2<br>CHAPTER 5                                                                                                                                                                                              | Simplified Receive Operation                                   |

| CHAPTER 5                                                                                                                                                                                                       | LOGIC DESCRIPTION                                              |

| CHAPTER 5                                                                                                                                                                                                       | LOGIC DESCRIPTION<br>EBUS INTERFACE AND PORT ALU MODULE        |

| CHAPTER 5<br>5.1<br>5.1.1                                                                                                                                                                                       | LOGIC DESCRIPTION<br>EBUS INTERFACE AND PORT ALU MODULE        |

| CHAPTER 5<br>5.1<br>5.1.1<br>5.1.2                                                                                                                                                                              | LOGIC DESCRIPTION<br>EBUS INTERFACE AND PORT ALU MODULE        |

| CHAPTER 5<br>5.1<br>5.1.1<br>5.1.2<br>5.1.3                                                                                                                                                                     | LOGIC DESCRIPTION<br>EBUS INTERFACE AND PORT ALU MODULE        |

| CHAPTER 5<br>5.1<br>5.1.1<br>5.1.2                                                                                                                                                                              | LOGIC DESCRIPTION<br>EBUS INTERFACE AND PORT ALU MODULE        |

| CHAPTER 5<br>5.1<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.3.1                                                                                                                                                          | LOGIC DESCRIPTION<br>EBUS INTERFACE AND PORT ALU MODULE        |

| CHAPTER 5<br>5.1<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.3.1<br>5.1.3.2<br>5.1.3.2.1<br>5.1.3.2.1<br>5.1.3.2.2                                                                                                        | LOGIC DESCRIPTION<br>EBUS INTERFACE AND PORT ALU MODULE        |

| CHAPTER 5<br>5.1<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.3.1<br>5.1.3.2<br>5.1.3.2.1<br>5.1.3.2.1<br>5.1.3.2.2<br>5.1.4                                                                                               | LOGIC DESCRIPTION<br>EBUS INTERFACE AND PORT ALU MODULE        |

| CHAPTER 5<br>5.1<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.3.1<br>5.1.3.2<br>5.1.3.2.1<br>5.1.3.2.1<br>5.1.3.2.1<br>5.1.3.2.2<br>5.1.4<br>5.1.5                                                                         | LOGIC DESCRIPTION<br>EBUS INTERFACE AND PORT ALU MODULE        |

| CHAPTER 5<br>5.1<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.3.1<br>5.1.3.2<br>5.1.3.2.1<br>5.1.3.2.1<br>5.1.3.2.2<br>5.1.4<br>5.1.5<br>5.1.6                                                                             | LOGIC DESCRIPTION<br>EBUS INTERFACE AND PORT ALU MODULE        |

| CHAPTER 5<br>5.1<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.3.1<br>5.1.3.2<br>5.1.3.2.1<br>5.1.3.2.1<br>5.1.3.2.1<br>5.1.3.2.2<br>5.1.4<br>5.1.5<br>5.1.6<br>5.1.7                                                       | LOGIC DESCRIPTION<br>EBUS INTERFACE AND PORT ALU MODULE        |

| CHAPTER 5<br>5.1<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.3.1<br>5.1.3.2<br>5.1.3.2<br>5.1.3.2.1<br>5.1.3.2.1<br>5.1.3.2.1<br>5.1.3.2.2<br>5.1.4<br>5.1.5<br>5.1.6<br>5.1.7<br>5.1.8                                   | LOGIC DESCRIPTION<br>EBUS INTERFACE AND PORT ALU MODULE        |

| CHAPTER 5<br>5.1<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.3.1<br>5.1.3.2<br>5.1.3.2.1<br>5.1.3.2.1<br>5.1.3.2.1<br>5.1.3.2.2<br>5.1.4<br>5.1.5<br>5.1.6<br>5.1.7<br>5.1.8<br>5.1.9                                     | LOGIC DESCRIPTION<br>EBUS INTERFACE AND PORT ALU MODULE        |

| CHAPTER 5<br>5.1<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.3.1<br>5.1.3.2<br>5.1.3.2.1<br>5.1.3.2.1<br>5.1.3.2.1<br>5.1.3.2.2<br>5.1.4<br>5.1.5<br>5.1.6<br>5.1.7<br>5.1.8<br>5.1.9<br>5.1.10                           | LOGIC DESCRIPTION<br>EBUS INTERFACE AND PORT ALU MODULE        |

| CHAPTER 5<br>5.1<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.3.1<br>5.1.3.2<br>5.1.3.2.1<br>5.1.3.2.1<br>5.1.3.2.1<br>5.1.3.2.2<br>5.1.4<br>5.1.5<br>5.1.6<br>5.1.7<br>5.1.8<br>5.1.9<br>5.1.10<br>5.1.11                 | LOGIC DESCRIPTION<br>EBUS INTERFACE AND PORT ALU MODULE        |

| CHAPTER 5<br>5.1<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.3.1<br>5.1.3.2<br>5.1.3.2.1<br>5.1.3.2.1<br>5.1.3.2.1<br>5.1.3.2.2<br>5.1.4<br>5.1.5<br>5.1.6<br>5.1.7<br>5.1.8<br>5.1.9<br>5.1.10<br>5.1.11<br>5.2          | LOGIC DESCRIPTION<br>EBUS INTERFACE AND PORT ALU MODULE        |

| CHAPTER 5<br>5.1<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.3.1<br>5.1.3.2<br>5.1.3.2.1<br>5.1.3.2.1<br>5.1.3.2.1<br>5.1.3.2.2<br>5.1.4<br>5.1.5<br>5.1.6<br>5.1.7<br>5.1.8<br>5.1.9<br>5.1.10<br>5.1.11                 | LOGIC DESCRIPTION<br>EBUS INTERFACE AND PORT ALU MODULE        |

| CHAPTER 5<br>5.1<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.3.1<br>5.1.3.2<br>5.1.3.2.1<br>5.1.3.2.1<br>5.1.3.2.1<br>5.1.3.2.2<br>5.1.4<br>5.1.5<br>5.1.6<br>5.1.7<br>5.1.8<br>5.1.9<br>5.1.10<br>5.1.11<br>5.2<br>5.2.1 | LOGIC DESCRIPTION<br>EBUS INTERFACE AND PORT ALU MODULE        |

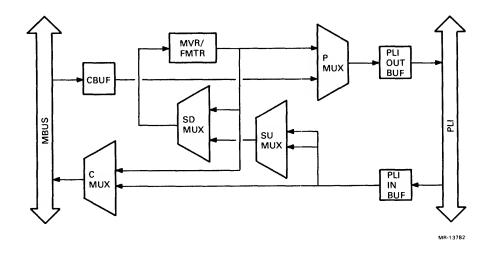

| 5.2.5      | PLI Serial Down Multiplexer (SDMUX)5-34        |

|------------|------------------------------------------------|

| 5.2.6      | PLI Output Multiplexer (PMUX)                  |

| 5.2.7      | CMVR to Microprocessor Multiplexer (CMUX)5-35  |

| 5.2.8      | Microprocessor to CMVR Register (CBUF)         |

| 5.2.9      | CBus Input Buffer                              |

| 5.2.10     | CBus In Parity Checker                         |

| 5.2.11     | CBus Output Buffer                             |

| 5.2.12     | CBus Out Parity Generator                      |

| 5.2.13     | CBus Control Logic                             |

| 5.2.14     | PLI Input Buffer                               |

| 5.2.15     | PLI Parity In Checker                          |

| 5.2.16     | PLI Output Buffer                              |

| 5.2.17     | PLI Parity Out Generator                       |

| 5.2.18     | PLI Control Logic                              |

| 5.2.19     | Parity Predictor                               |

| 5.3        | PORT MICROPROCESSOR                            |

| 5.3.1      | Condition Code Multiplexer                     |

| 5.3.2      | Microsequencer                                 |

| 5.3.3      | RAM Address Register                           |

| 5.3.4      | Latch Address Register                         |

| 5.3.5      | Address Multiplexer                            |

| 5.3.6      | Control RAM                                    |

| 5.3.7      | CRAM Load Buffers                              |

| 5.3.8      | CRAM Parity Checker                            |

| 5.3.9      | CRAM Register                                  |

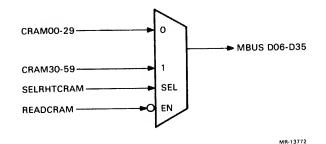

| 5.3.10     | Microword Field Definitions                    |

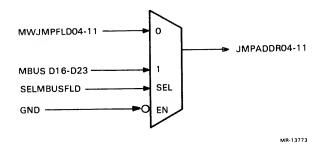

| 5.3.11     | Microword Output Multiplexer                   |

| 5.3.12     | Jump Multiplexer                               |

| 5.3.13     | Local Storage RAM                              |

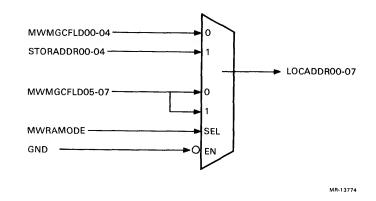

| 5.3.14     | RAM Mode Multiplexer                           |

| 5.3.15     | Local Storage Address Register                 |

| 5.3.16     | Skip Condition Field Decoder                   |

| 5.3.17     | Microprocessor Control Logic                   |

| 5.4        | MICROCODE                                      |

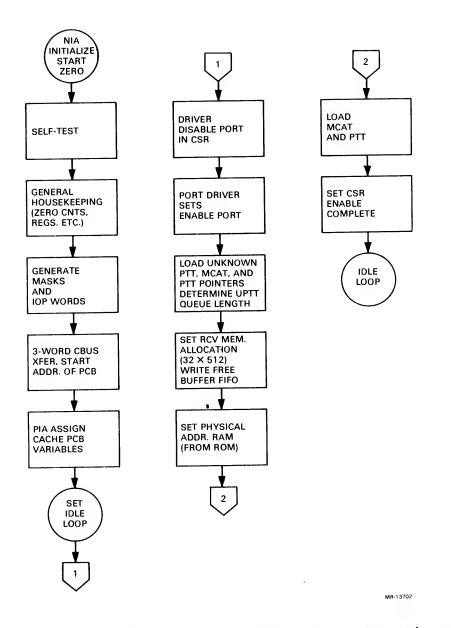

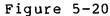

| 5.4.1      | Initialization                                 |

| 5.4.2      |                                                |

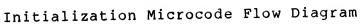

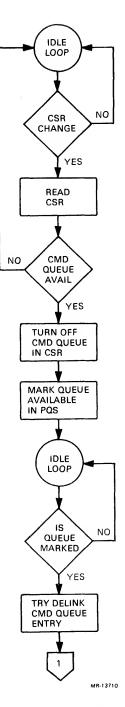

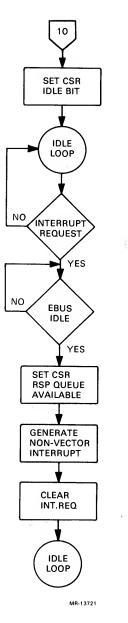

| 5.4.3      | Idle Loop                                      |

| 5.4.4      | Receive                                        |

| 5.4.4      |                                                |

| APPENDIX A | INSTALLATION OF NIA20 IN KL10-D                |

| A.1        | OVERVIEW                                       |

| A.2        | UNPACKING AND CHECKOUT                         |

| A.3        | EQUIPMENT NEEDED FOR INSTALLATION AND CHECKOUT |

| A.4        | INSTALLATION PROCEDURE                         |

|            |                                                |

| A.4.1   | Preinstallation Checkout                     |

|---------|----------------------------------------------|

| A.4.2   | Backplane Wire Adds                          |

| A.4.3   | Installation of Port Modules                 |

| A.4.4   | Power Supply Regulator Installation          |

| A.4.5   | Installation of NIA20 Card Cage/Cable        |

| A.4.5.1 | Installation of NIA20 Current Limiter        |

| A.4.5.2 | Harness Installation                         |

| A.4.6   | Installation of KLlO Adapter Board and Blank |

|         | Module Assembly                              |

| A.4.7   | CheckoutA-24                                 |

## APPENDIX B INSTALLATION OF NIA20 IN KL10-R

| B.1     | OVERVIEWB-1                                        |

|---------|----------------------------------------------------|

| B.2     | UNPACKING AND CHECKOUTB-7                          |

| B.3     | EQUIPMENT NEEDED FOR INSTALLATION AND CHECKOUTB-7  |

| B.4     | INSTALLATION PROCEDURE                             |

| B.4.1   | Preinstallation CheckoutB-8                        |

| B.4.2   | Backplane Wire AddsB-8                             |

| B.4.3   | Installation of Port ModulesB-9                    |

| B.4.4   | Power Supply Regulator InstallationB-13            |

| B.4.5   | Installation of NIA20 Card Cage/Internal CableB-13 |

| B.4.5.1 | Installation of NIA20 Current LimiterB-17          |

| B.4.5.2 | Harness Installation                               |

| В.4.6   | Installation of KL10 Adapter Board and Blank       |

|         | Module AssemblyB-24                                |

| B.4.7   | CheckoutB-25                                       |

#### FIGURES

## Figure No.

## Title

## Page

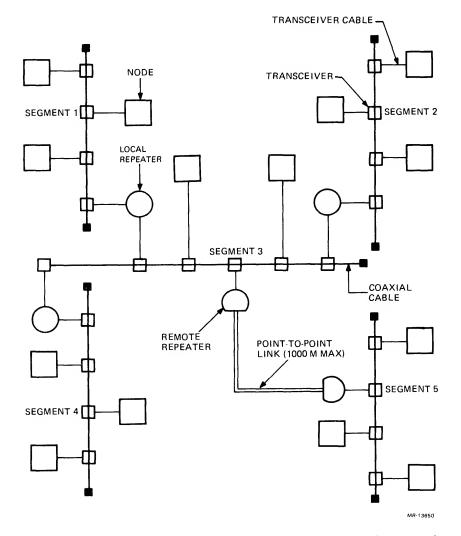

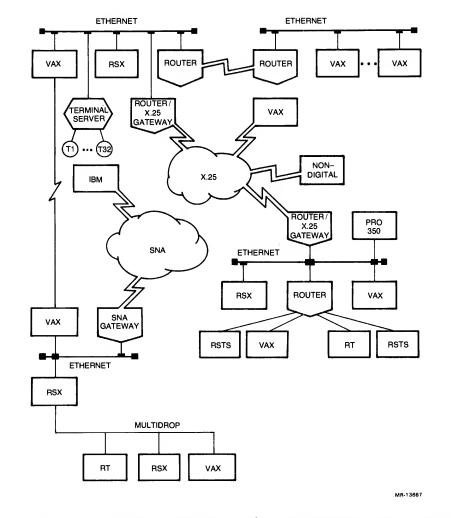

| 1-1  | Large-Scale Ethernet Configuration              |

|------|-------------------------------------------------|

| 1-2  | Simplified NIA20 Block Diagram                  |

| 1-3  | Ethernet Data Packet Format                     |

| 1-4  | Manchester Encodingl-11                         |

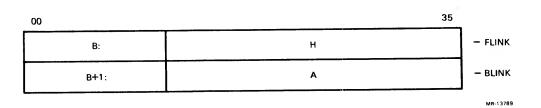

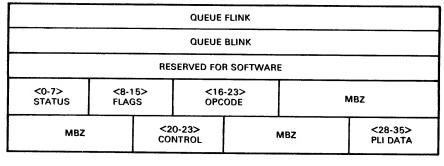

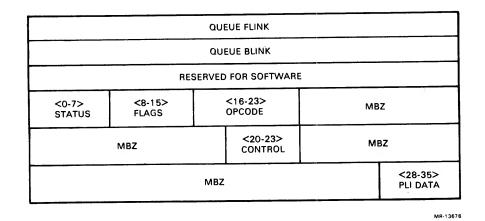

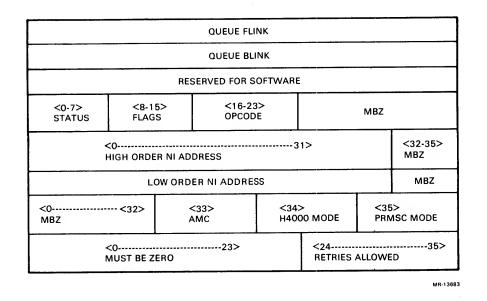

| 2-1  | Queue Entry Format                              |

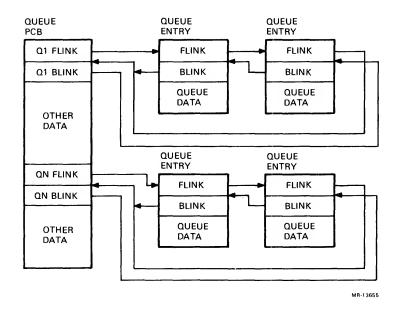

| 2-2  | Queue Linkage2-2                                |

| 2-3  | KL10 Memory PCB Format                          |

| 2-4  | Error Word 3 Format                             |

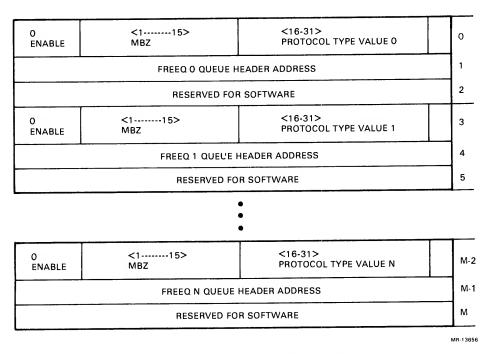

| 2-5  | Protocol Type Table Format                      |

| 2-6  | Multicast Address Table Format                  |

| 2-7  | Queue Header Format2-8                          |

| 2-8  | Use of Queue Headers2-9                         |

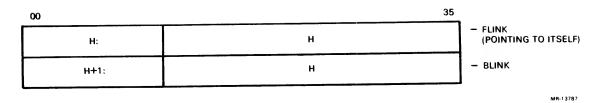

| 2-9  | Empty Queue                                     |

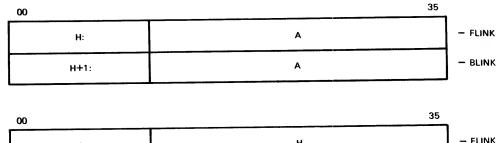

| 2-10 | Queue with Entry at Address A2-10               |

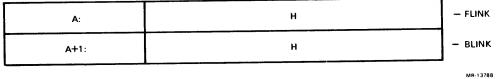

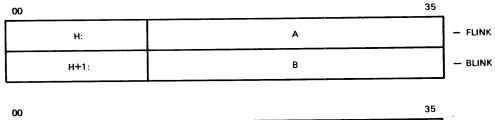

| 2-11 | Entry at Address B at the Tail of the Queue2-10 |

| 2-12 | Entry at Address C at the Tail of the Queue2-11 |

| Page | e |

|------|---|

|------|---|

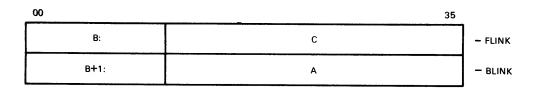

| 2-13 | Queue Containing Entries A, B, and C, Where<br>A Can Be Removed2-12 |

|------|---------------------------------------------------------------------|

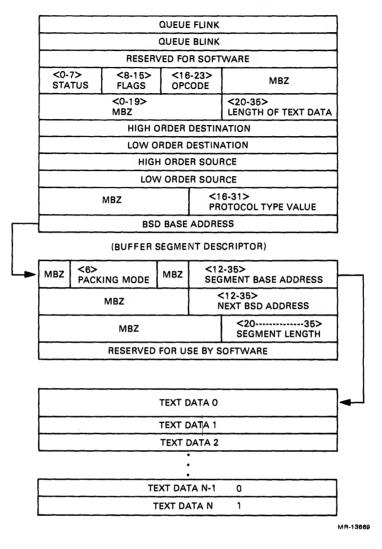

| 2-14 | BSD Format,                                                         |

| 2-15 | SNDDG Command Format (BSD)                                          |

| 2-16 | SNDDG Command Format (Non-BSD)                                      |

| 2-17 | Send Datagram                                                       |

| 2-18 | Non-Send Datagram                                                   |

| 2-19 | Non-Send Datagram                                                   |

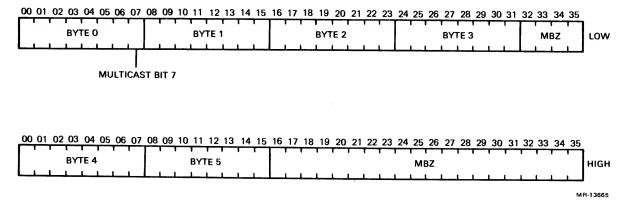

| 2-20 | Destination Address Format                                          |

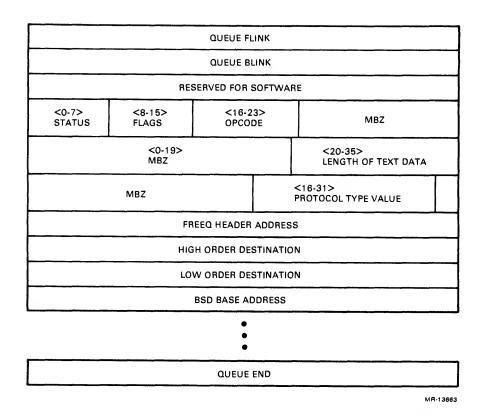

| 2-20 | DGSNT Response Format (Non-BSD)                                     |

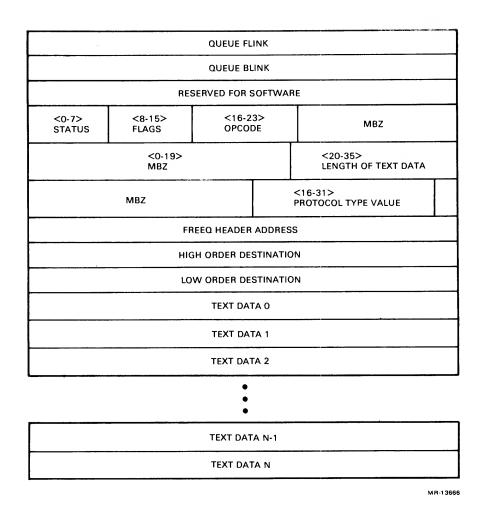

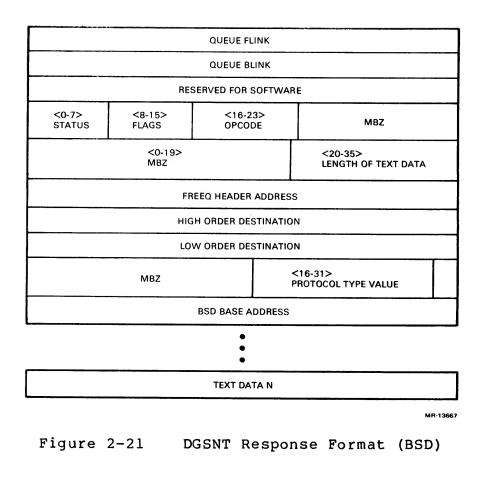

| 2-22 | DGSNT Response Format (BSD)                                         |

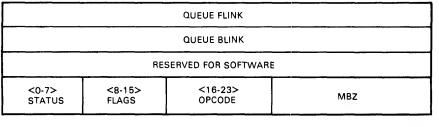

| 2-23 | Status Field from Queue                                             |

| 2-24 | DGRCV Response Format                                               |

| 2-25 | LDPTT Command Format                                                |

| 2-26 | PTTLD Response Format                                               |

| 2-27 | LDMCAT Command Format                                               |

| 2-28 | MCATLD Response Format                                              |

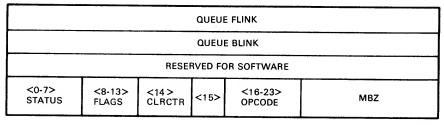

| 2-29 | RCCNT Command Format                                                |

| 2-30 | CNTCL Response Format                                               |

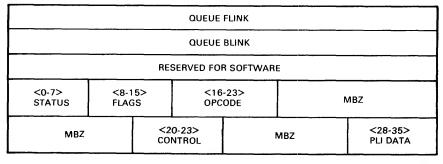

| 2-31 | WRTPLI Command Format                                               |

| 2-32 | PLIWRT Response Format                                              |

| 2-33 | RDPLI Command Format                                                |

| 2-34 | PLIRD Response Format                                               |

| 2-35 | RDNSA Command Format                                                |

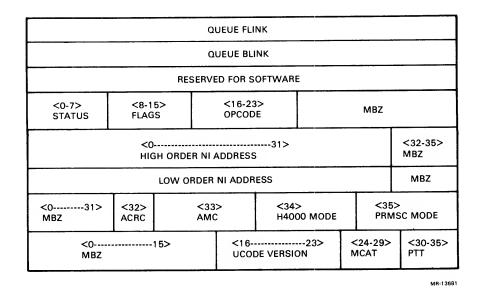

| 2-36 | RDNSA Response Format                                               |

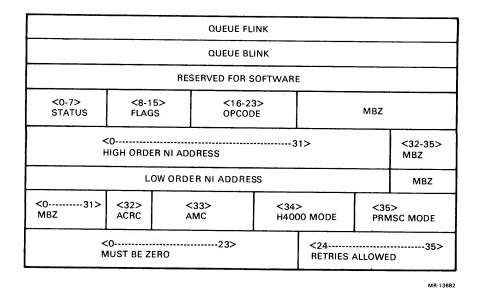

| 2-37 | WRTNSA Command Format                                               |

| 2-38 | NSAWRT Response Format                                              |

| 2-39 | KL10 Word (Industry-Compatible Mode)                                |

| 2-40 | Digital Network Architecture (DNA)                                  |

|      | Functional Layers                                                   |

| 2-41 | DNA Layers and Interfaces                                           |

| 2-42 | DECnet Network with Many Ethernet Segments2-46                      |

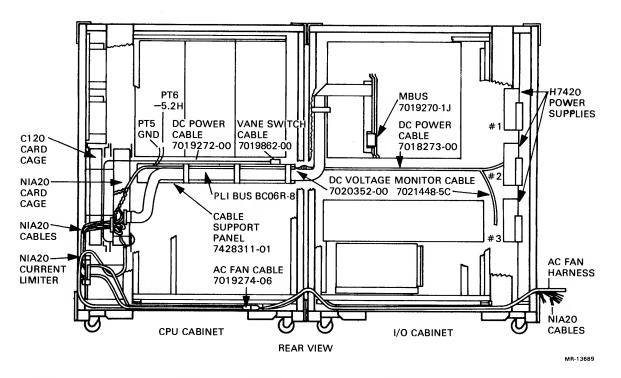

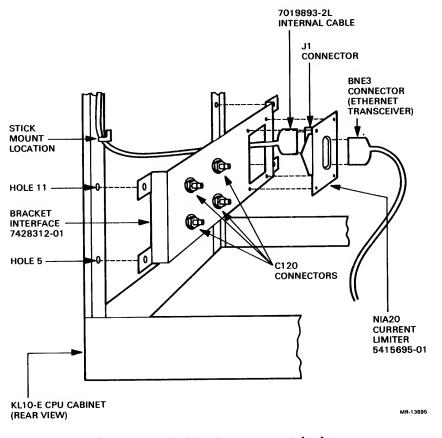

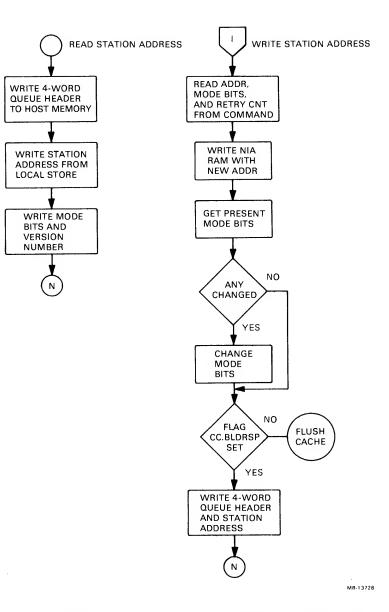

| 3-1  | NIA20 in KL10-E, Rear View                                          |

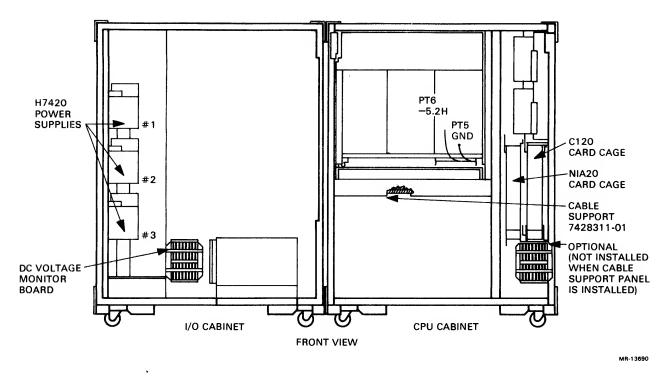

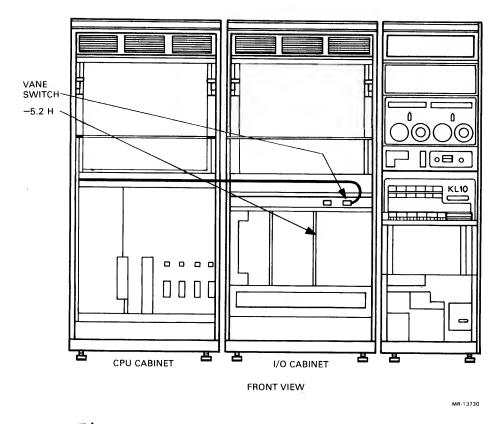

| 3-2  | NIA20 in KL10-E, Front View                                         |

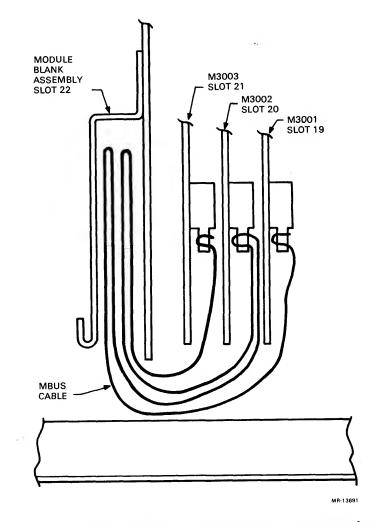

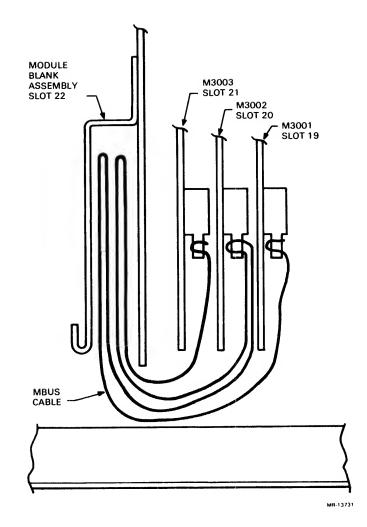

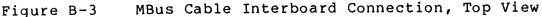

| 3-3  | MBus Cable Interboard Connection, Top View                          |

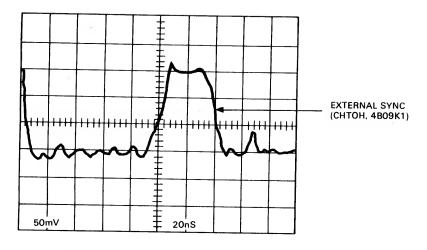

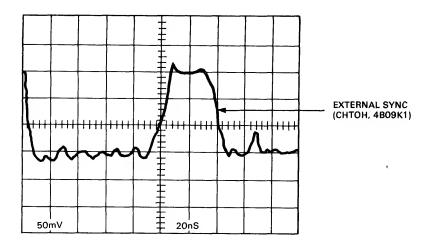

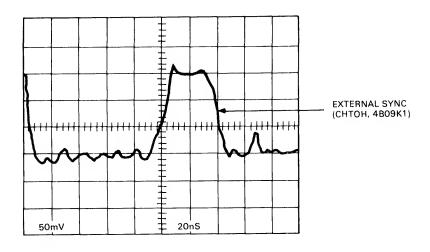

| 3-4  | NIA20 De-skew Timing. External Sync (CHTO H)3-11                    |

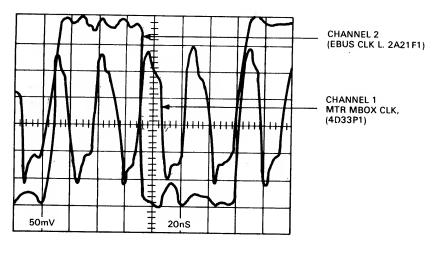

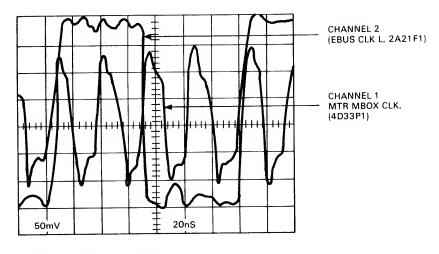

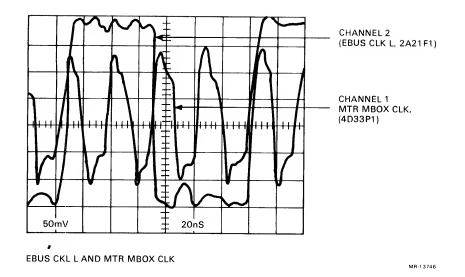

| 3-5  | NIA20 De-skew Timing. EBUS CLK L and                                |

|      | MTR MBOX CLK                                                        |

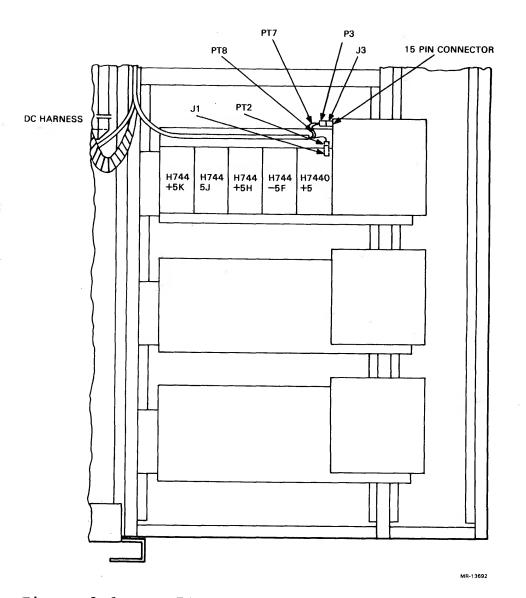

| 3-6  | H7420 Power Supply                                                  |

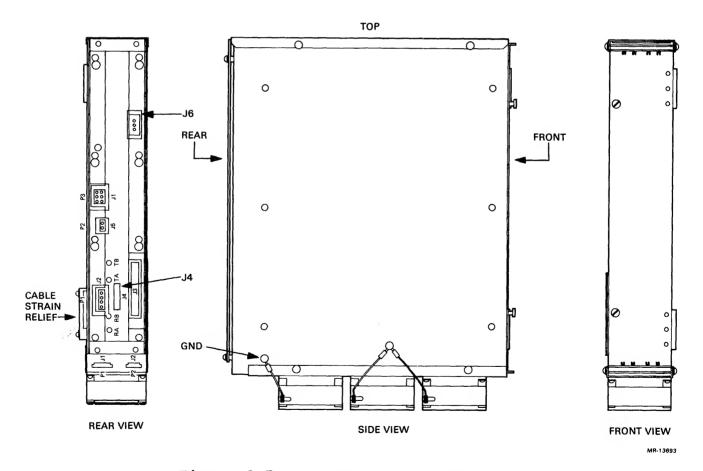

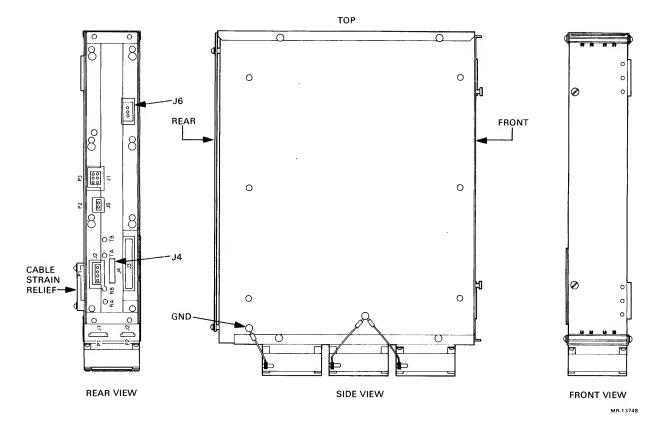

| 3-7  | NIA20 Card Cage Views                                               |

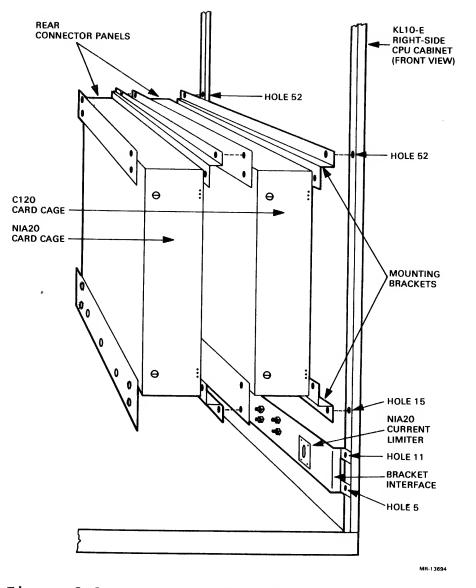

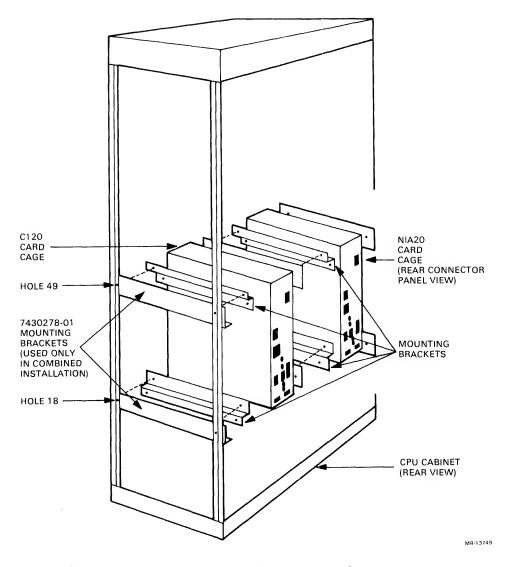

| 3-8  | NIA20 Card Cage in KL10-E3-15                                       |

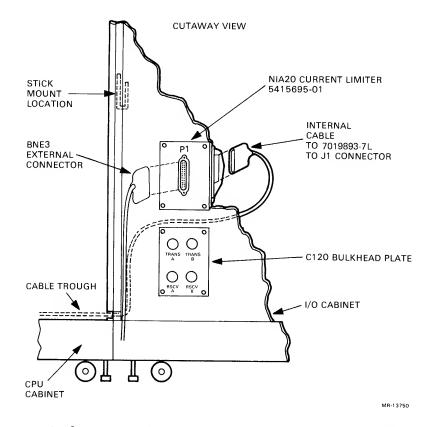

| 3-9  | NIA20 Current Limiter                                               |

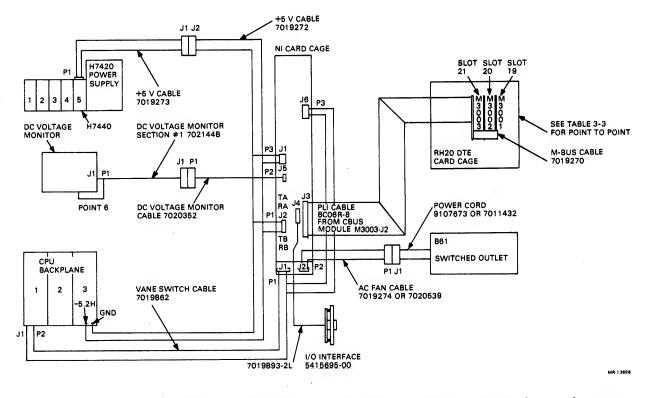

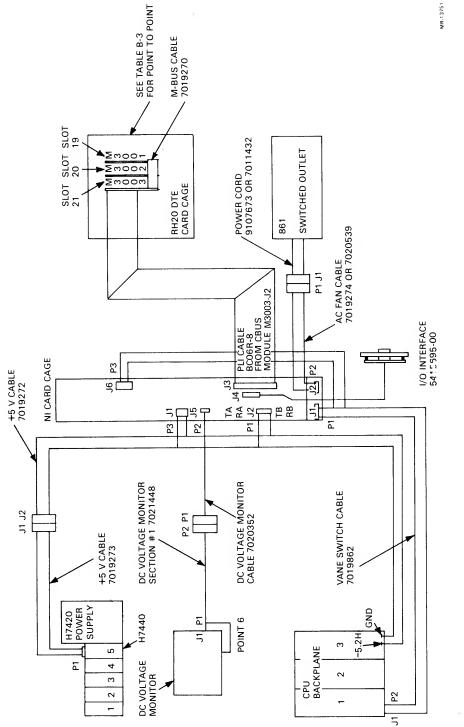

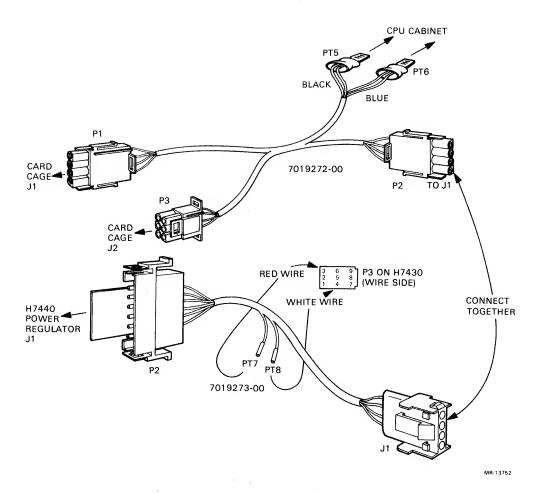

| 3-10 | NIA20 Harness and Cable Interconnection Diagram3-18                 |

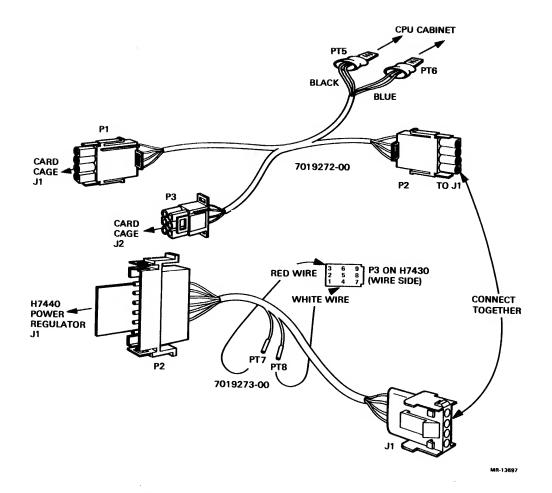

| 3-11 | DC Power Cable                                                      |

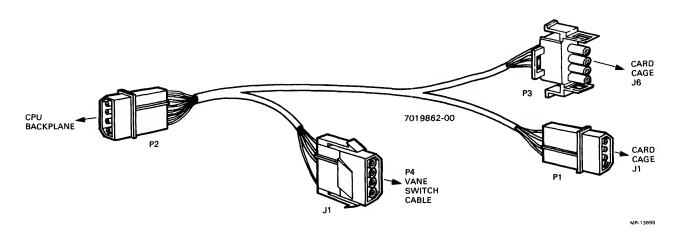

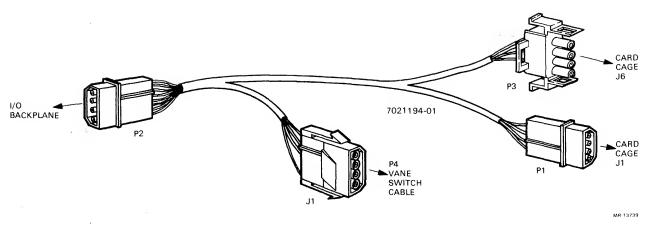

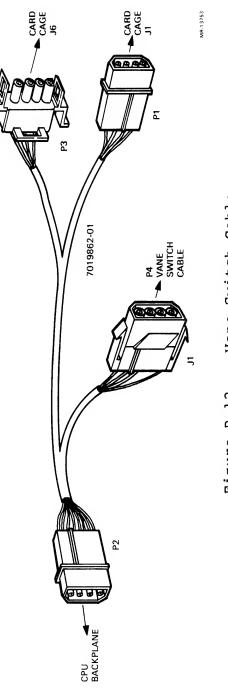

| 3-12 | Vane Switch Cable                                                   |

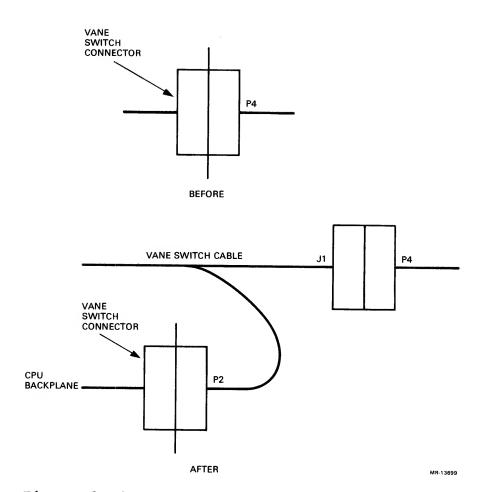

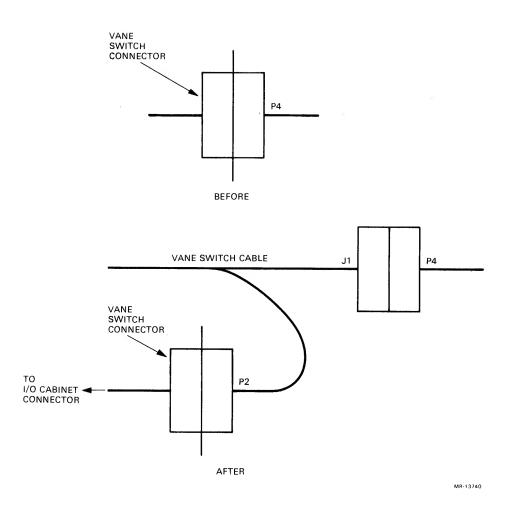

| 3-13 | Vane Switch Harness Installation                                    |

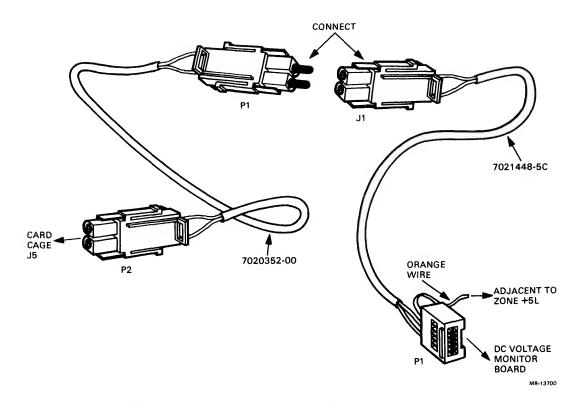

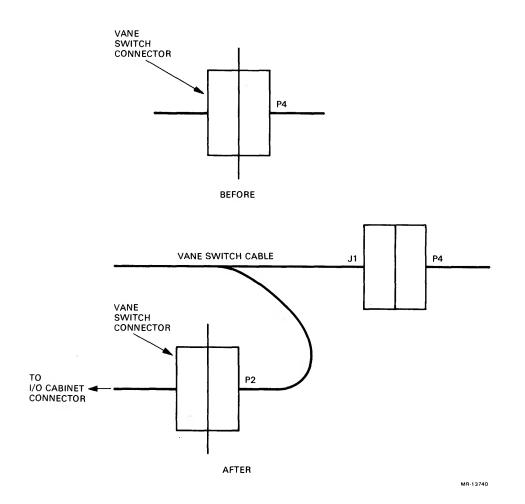

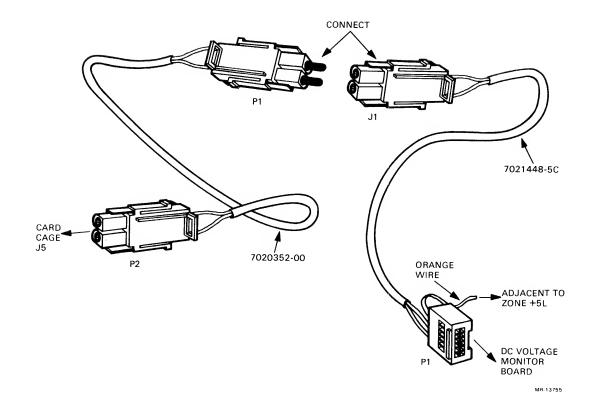

| 3-14 | DC Voltage Monitor Cable                                            |

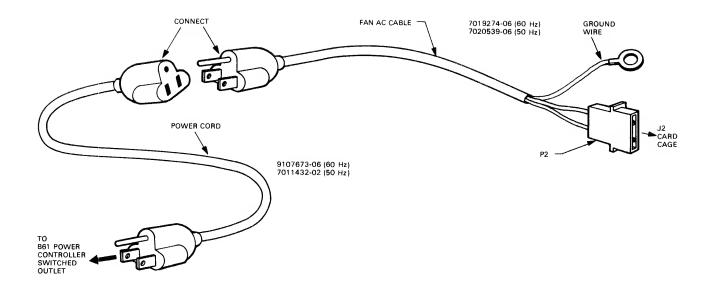

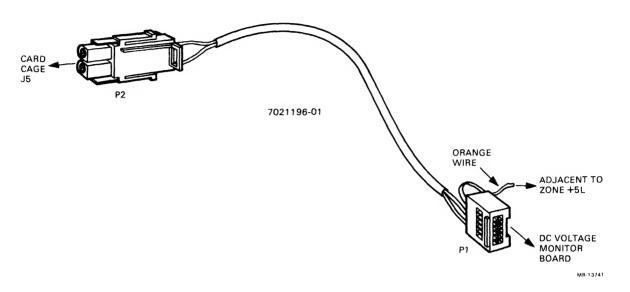

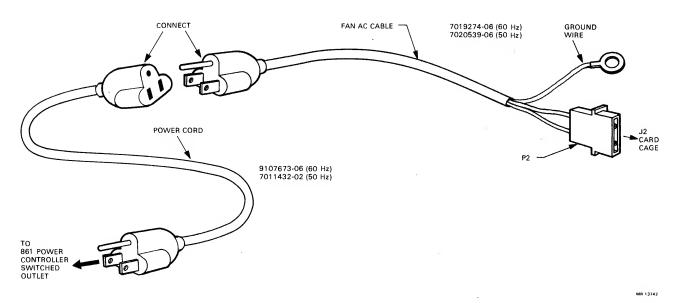

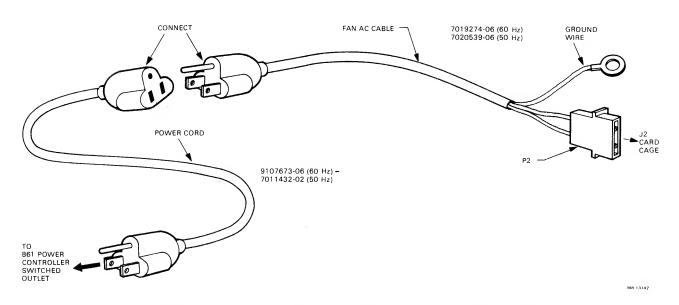

| 3-15 | Fan AC Cable and Power Cord                                         |

Page

| 4-1     | Port Control and Status Register4-2                 |

|---------|-----------------------------------------------------|

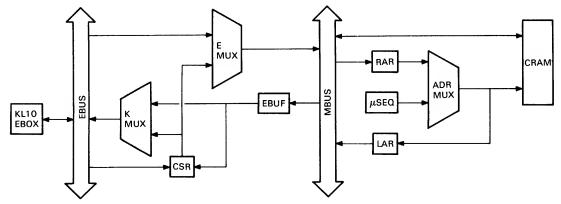

| 4-2     | EBus-to-Port Simplified Block Diagram4-6            |

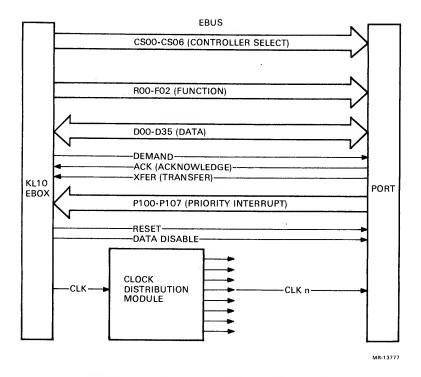

| 4-3     | EBus Signals4-7                                     |

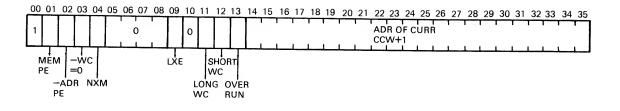

| 4-4     | IOP Function Control Word                           |

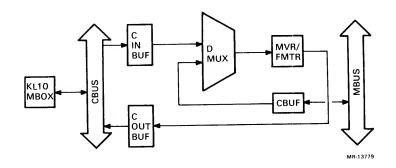

| 4-5     | CBus-to-Port Simplified Block Diagram               |

| 4-6     |                                                     |

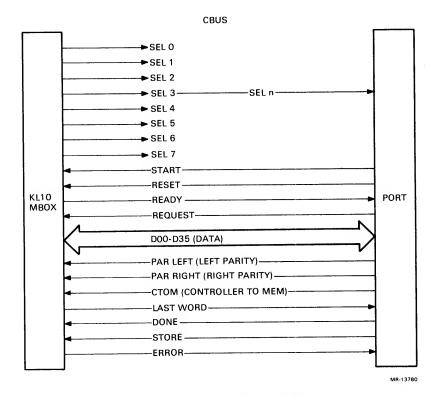

| 4-7     | CBus Signals                                        |

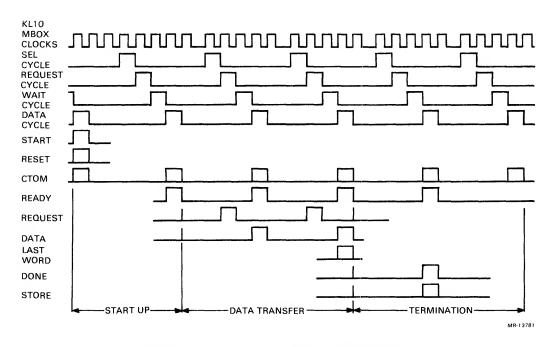

| 4-8     | CBus Operation                                      |

|         | PLI-to-Port Simplified Block Diagram4-20            |

| 4-9     | Clock Timing                                        |

| 4-10    | Simplified NIA Block Diagram                        |

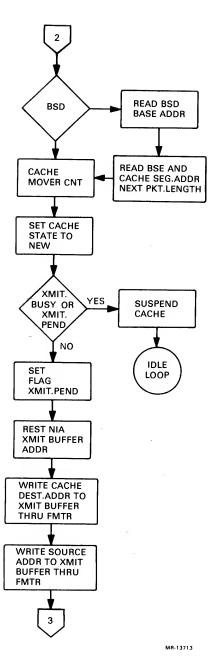

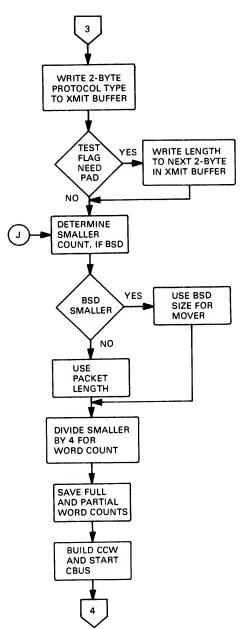

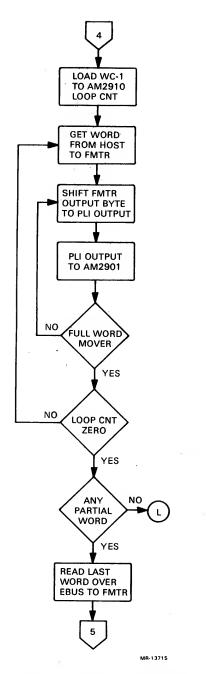

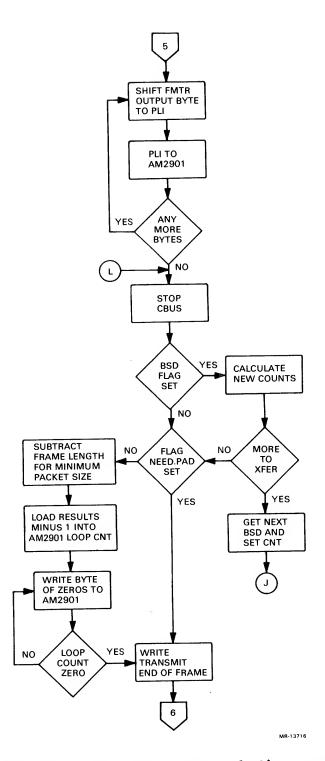

| 4-11    | PLI Interface Transmit Flow Diagram4-31             |

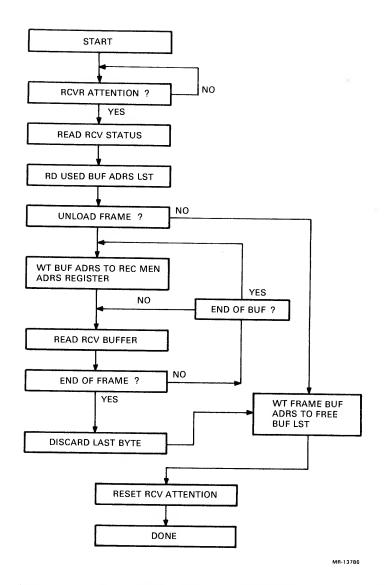

| 4-12    | PLI Interface Receive Flow Diagram                  |

| 5-1     | CSR Bits                                            |

| 5-2     | IOP Function Control Word                           |

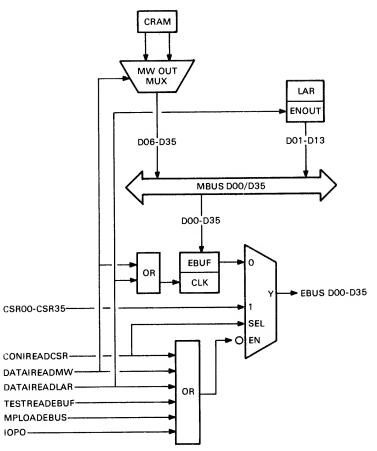

| 5-3     | EBus to Microprocessor Multiplexer                  |

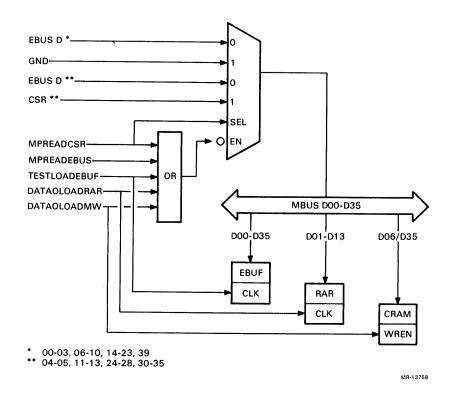

| 5-4     | Microprocessor to EBus Multiplexer                  |

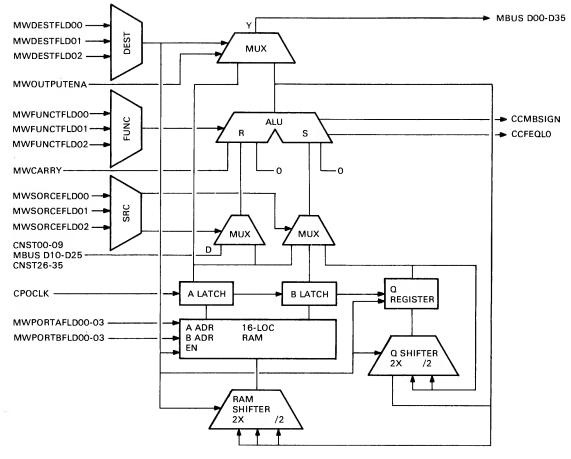

| 5-5     | AM2901 ALU Block Diagram (Simplified)               |

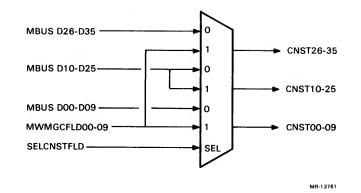

| 5-6     | Constant Multiplexer (Simplified)                   |

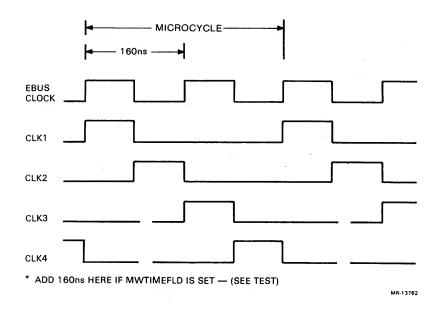

| 5-7     | Port Clock Timing                                   |

| 5-8     | Port Clock Timing                                   |

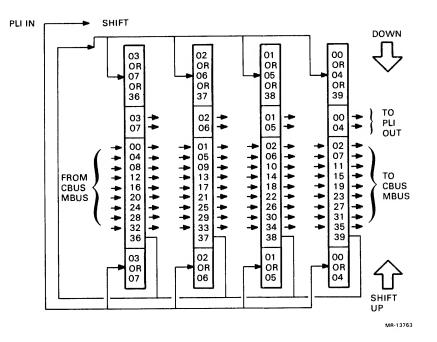

| 5-8     | Mover/Formatter Data Flow                           |

|         | DMUX (Simplified)                                   |

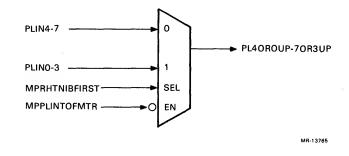

| 5-10    | SUMUX (Simplified)                                  |

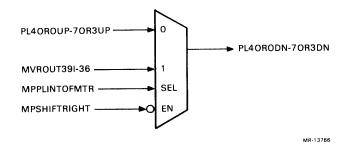

| 5-11    | SDMUX (Simplified)                                  |

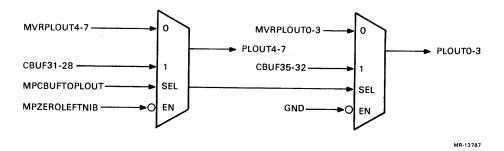

| 5-12    | PMUX (Simplified)                                   |

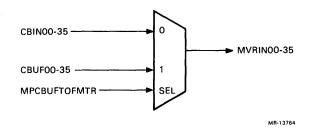

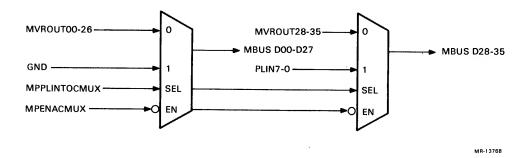

| 5-13    | CMUX (Simplified)                                   |

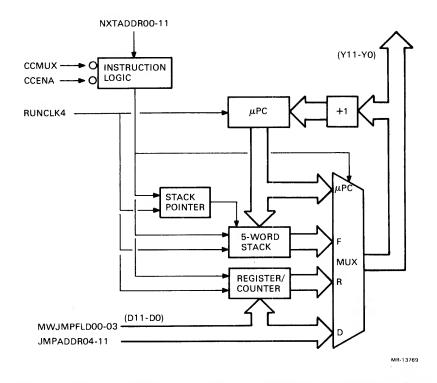

| 5-14    | Am2910 Block Diagram (Simplified)                   |

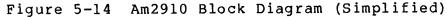

| 5-15    | Address Multiplexer (Simplified)                    |

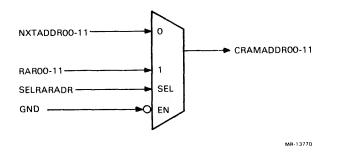

| 5-16    | CRAM Load Buffers (Simplified)                      |

| 5-17    | Microword Output Multiplexer (Simplified)           |

| 5-18    | Jump Multiplexer (Simplified)                       |

| 5-19    | RAM Mode Multiplexer (Simplified)                   |

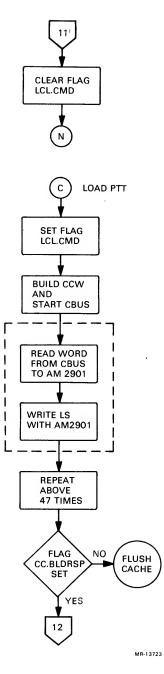

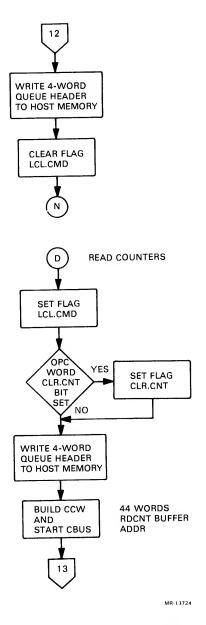

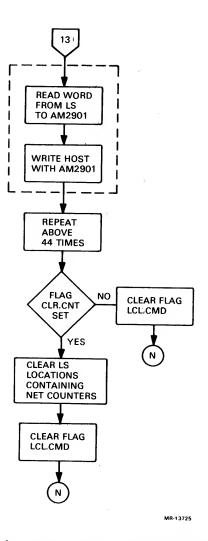

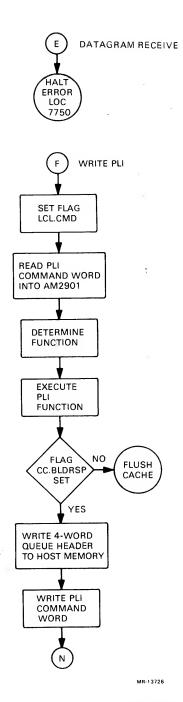

| 5-20    | Initialization Microcode Flow Diagram               |

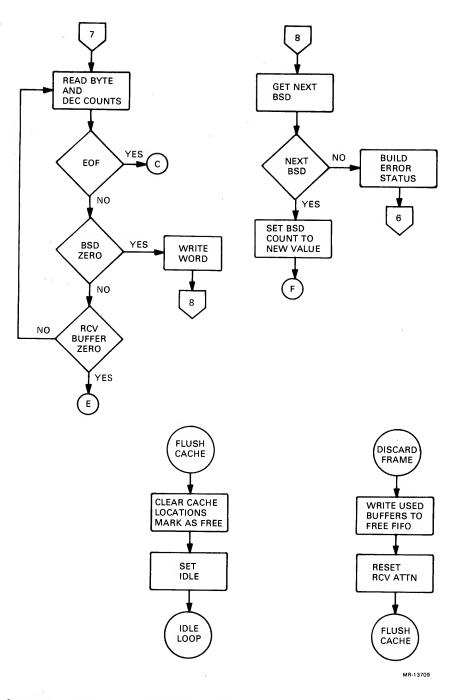

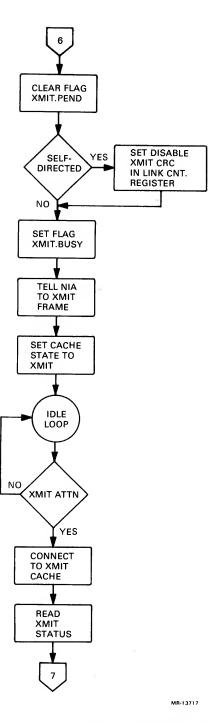

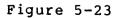

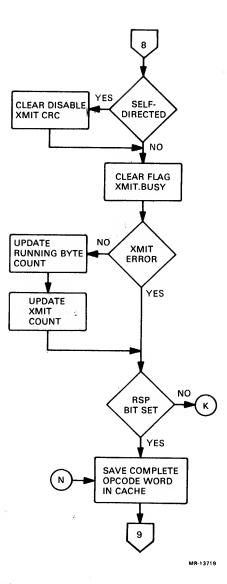

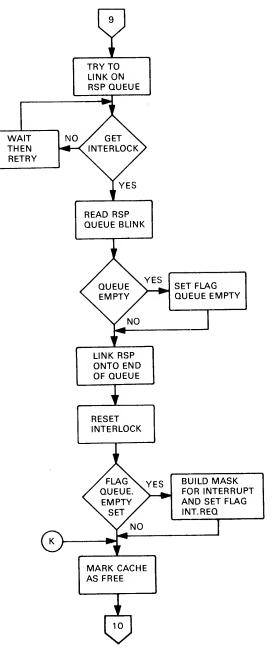

| 5-21    | Idle Loop Microcode Flow Diagram                    |

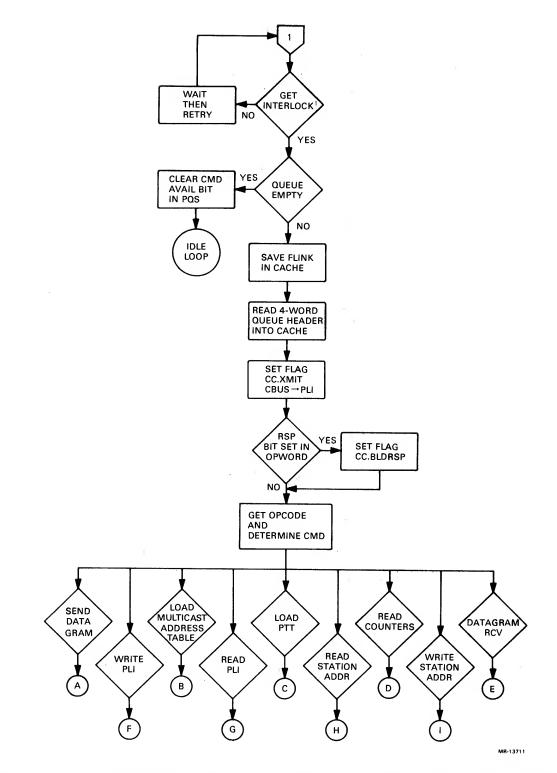

| 5-22    |                                                     |

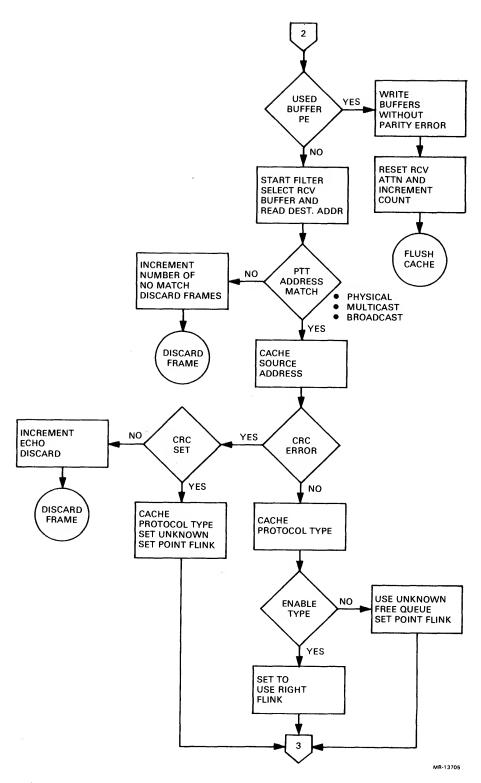

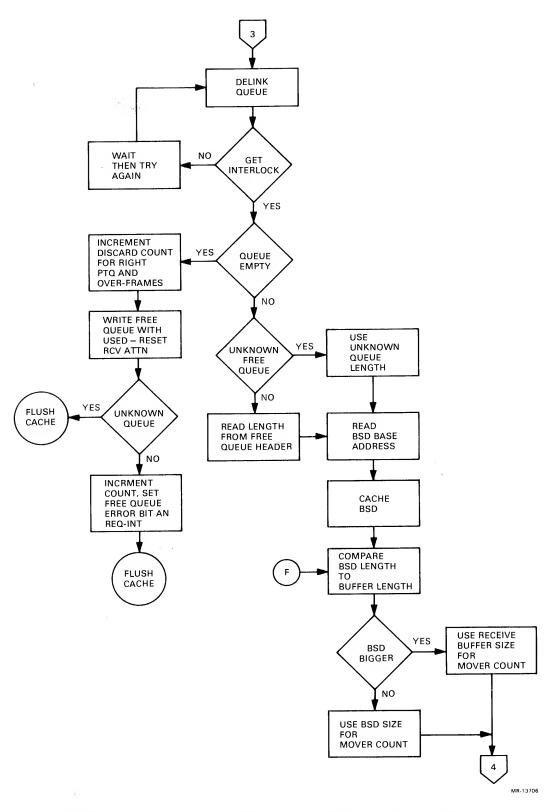

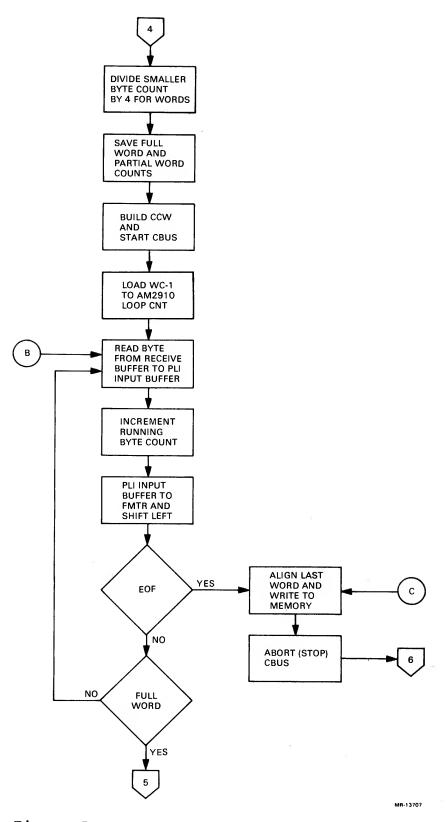

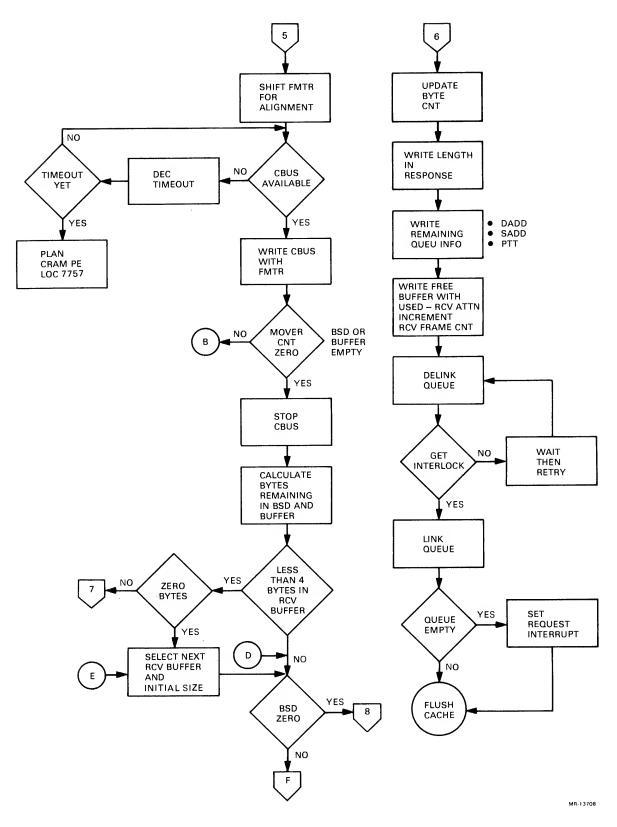

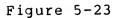

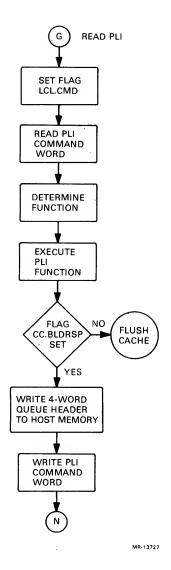

| 5-23    | Receive Microcode Flow Diagram                      |

| J-2J    | Transmit and Local Command Microcode                |

| x 1     | Flow Diagram                                        |

| A-1     | NIA20 in KL10-D, Rear View                          |

| A-2     | NIA20 in KL10-D, Front View                         |

| A-3     | MBus Cable Interboard Connection, Top ViewA-10      |

| A-4     | NIA De-skew Timing. External Sync (CHTO H) A-11     |

| A-5     | NIA20 De-skew Timing. EBus CLK L and                |

|         | MTR MBOX CLK                                        |

| А-б     | H7420 Power Supply                                  |

| A-7     | NIA20 Card Cage in KL10-DA-15                       |

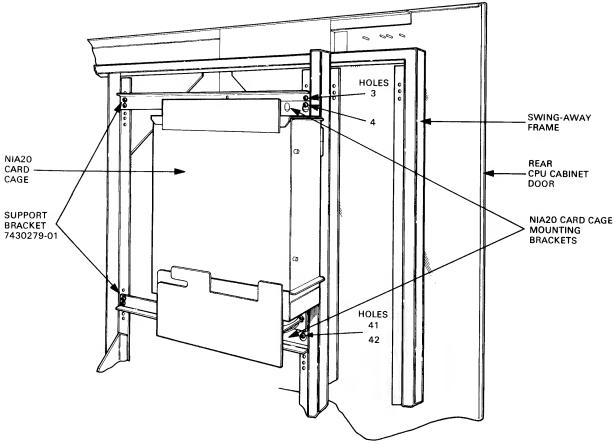

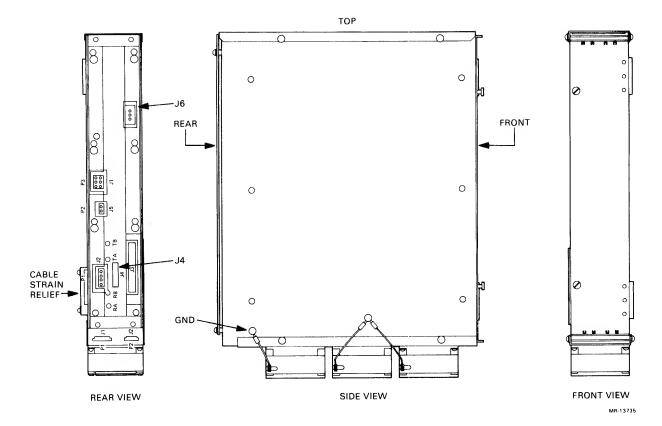

| A-8     | NIA20 Card Cage Views                               |

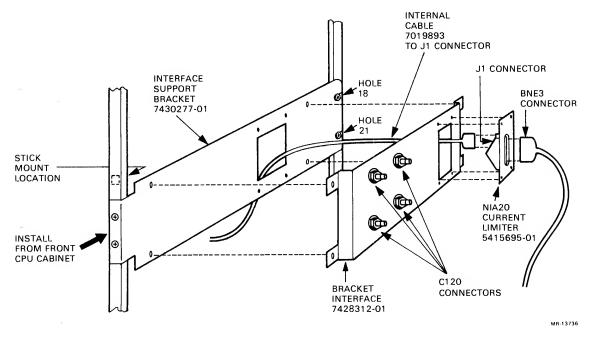

| A-9     | NIA20 Current Limiter                               |

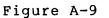

| A-10    | NIA20 Harness and Cable Interconnection DiagramA-18 |

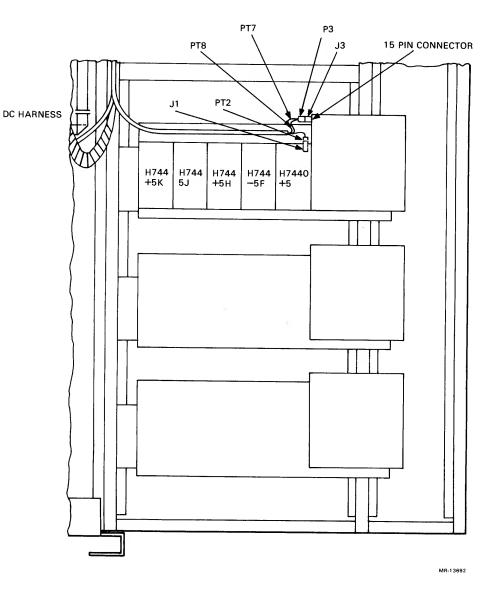

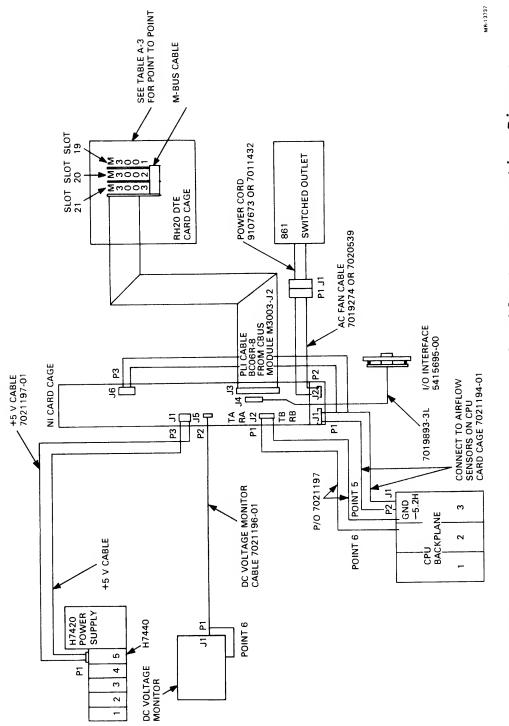

| A-11    | DC Power Cable                                      |

| 4 A A A |                                                     |

| Page |  |

|------|--|

|------|--|

| A-12 | Vane Switch Cable                                   |

|------|-----------------------------------------------------|

| A-13 | Vane Switch Harness Installation                    |

| A-14 | DC Voltage Monitor Cable                            |

| A-15 | Fan AC Cable and Power Cord                         |

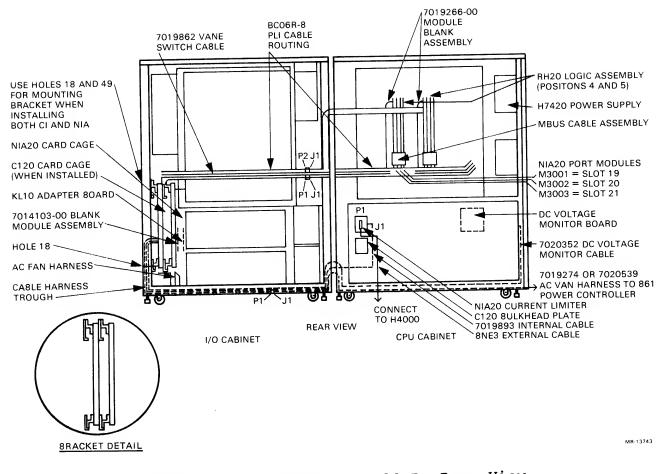

| B-1  | NIA20 in KL10-R, Rear ViewB-2                       |

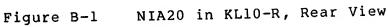

| B-2  | NIA20 in KL10-R, Front ViewB-3                      |

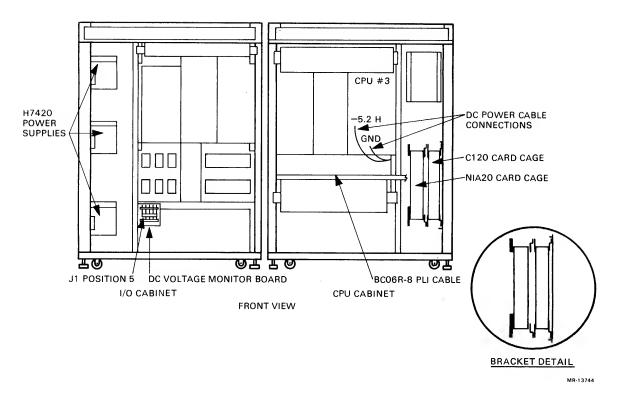

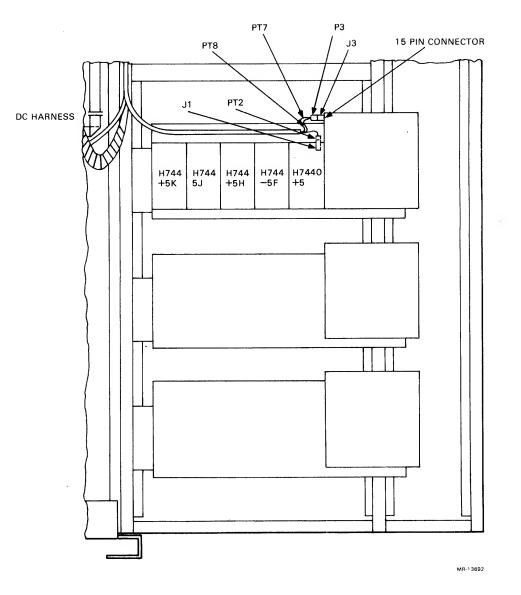

| B-3  | MBus Cable Interboard Connection, Top ViewB-10      |

| B-4  | NIA20 De-skew Timing. External Sync (CHTO H) B-12   |

| B-5  | NIA20 De-skew Timing. EBUS CLK L and                |

|      | MTR MBOX CLKB-13                                    |

| B-6  | H7420 Power SupplyB-14                              |

| B-7  | NIA20 Card Cage ViewsB-15                           |

| B-8  | NIA20 Card Cage in KL10-RB-16                       |

| B-9  | NIA20 Current Limiter, Cutaway ViewB-17             |

| B-10 | NIA20 Harness and Cable Interconnection DiagramB-20 |

| 8-11 | DC Power CableB-21                                  |

| B-12 | Vane Switch CableB-22                               |

| B-13 | Vane Switch Harness InstallationB-23                |

| B-14 | DC Voltage Monitor CableB-24                        |

| B-15 | Fan AC Cable and Power CordB-24                     |

|      |                                                     |

## TABLES

## Table No.

## Title

## Page

| 1-1  | H4000 Pin Assignments1-8                         |

|------|--------------------------------------------------|

| 2-1  | Error Word 3 Bit Descriptions2-5                 |

| 2-2  | Error Log and Type2-22                           |

| 2-3  | Transmission Failure Bit Mask Assignments2-30    |

| 2-4  | Reception Failure Bit Mask Assignments2-31       |

| 2-5  | Command Code Values and Functions2-33            |

| 2-6  | Control Bit Values and Functions2-35             |

| 2-7  | Possible Error Conditions2-40                    |

| 3-1  | Parts List, NIA20 in KL10-E3-1                   |

| 3-2  | NIA20 in KL10-E Harness and Cable Connections3-3 |

| 3-3  | NIA20 in KL10-E Wire Adds                        |

| 4-1  | Control and Status Register Bit Definitions4-3   |

| 4-2  | EBus Signal Description4-7                       |

| 4-3  | KL10 Diagnostic Functions4-9                     |

| 4-4  | IOP Function Control Word4-10                    |

| 4-5  | CSR Bit Description4-15                          |

| 4-6  | CBus Cycles4-18                                  |

| 4-7  | PLI Signals4-21                                  |

| 4-8  | Link Control Signals4-22                         |

| 4-9  | Transmit Action Command Group4-23                |

| 4-10 | Write Address Register Access Table4-26          |

| 5-2EBus Functions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |      |                                           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------------------------------------------|

| 5-3IOP Function Control Word Bit Description.5-165-4ALU Control Commands.5-245-5Decoder Output Signals.5-285-6Mover/Formatter Control Commands.5-305-7Condition Code Definitions.5-425-8Microsequencer Instructions.5-425-9Microword Field Definitions.5-455-10Skip/Condition Function.5-645-11Cache Base Addresses.5-675-12Local Store Address Register Command StatusBlock Offsets.5-685-13Command Queue Status Block Flag Word.5-685-14NIA20 in KL10-D Parts List.A-4A-2NIA20 in KL10-D, Harness and Cable Connections.A-5A-3NIA20 in KL10-R, Parts List.B-4B-2NIA20 in KL10-R, Harness and Cable Connections.B-6B-3MBus Cable Interboard Connection, Top View.B-10B-4NIA20 De-skew Timing. External Sync (CHT0 H).B-12B-5NIA20 Card Cage Views.B-13B-6H7420 Power Supply.B-14B-7NIA20 Card Cage Views.B-16B-9NIA20 Current Limiter, Cutaway View.B-17B-10NIA20 Harness and Cable Interconnection Diagram.B-20B-11DC Power Cable.B-21B-12Vane Switch Harness Installation.B-23B-14DC Voltage Monitor Cable.B-24 | 5-1  | CSR Bit Description                       |

| 5-4ALU Control Commands                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 5-2  | EBus Functions                            |

| 5-4ALU Control Commands                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 5-3  | IOP Function Control Word Bit Description |

| 5-5Decoder Output Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5-4  |                                           |

| 5-6Mover/Formatter Control Commands                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5-5  |                                           |

| 5-7Condition Code Definitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 5-6  |                                           |

| 5-8Microsequencer Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |                                           |

| 5-9Microword Field Definitions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | -    |                                           |

| 5-10Skip/Condition Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |                                           |

| 5-11Cache Base Addresses                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |                                           |

| 5-12Local Store Address Register Command Status<br>Block Offsets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |      |                                           |

| Block Offsets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |      |                                           |

| 5-13Command Queue Status Block Flag Word                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | • 10 |                                           |

| A-1NIA20 in KL10-D Parts List                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 5-13 |                                           |

| A-2NIA20 in KL10-D, Harness and Cable ConnectionsA-5A-3NIA20 in KL10-D Wire AddsA-8B-1NIA20 in KL10-R, Parts ListB-4B-2NIA20 in KL10-R, Harness and Cable ConnectionsB-5B-3MBus Cable Interboard Connection, Top ViewB-10B-4NIA20 De-skew Timing. External Sync (CHT0 H)B-12B-5NIA20 De-skew Timing. EBUS CLK L andMTR MBOX CLK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |      |                                           |

| A-3NIA20 in KL10-D Wire AddsA-8B-1NIA20 in KL10-R, Parts ListB-4B-2NIA20 in KL10-R, Harness and Cable ConnectionsB-5B-3MBus Cable Interboard Connection, Top ViewB-10B-4NIA20 De-skew Timing. External Sync (CHTO H)B-12B-5NIA20 De-skew Timing. EBUS CLK L andMTR MBOX CLK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |      |                                           |

| B-1NIA20 in KL10-R, Parts List                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |      |                                           |

| B-2NIA20 in KL10-R, Harness and Cable ConnectionsB-5B-3MBus Cable Interboard Connection, Top ViewB-10B-4NIA20 De-skew Timing. External Sync (CHT0 H)B-12B-5NIA20 De-skew Timing. EBUS CLK L and<br>MTR MBOX CLKB-13B-6H7420 Power SupplyB-14B-7NIA20 Card Cage ViewsB-15B-8NIA20 Card Cage in KL10-RB-16B-9NIA20 Current Limiter, Cutaway ViewB-17B-10NIA20 Harness and Cable Interconnection DiagramB-20B-11DC Power Cable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | B-1  |                                           |

| B-3MBus Cable Interboard Connection, Top ViewB-10B-4NIA20 De-skew Timing. External Sync (CHTO H)B-12B-5NIA20 De-skew Timing. EBUS CLK L andMTR MBOX CLKB-13B-6H7420 Power SupplyB-7NIA20 Card Cage ViewsB-8NIA20 Card Cage in KL10-RB-9NIA20 Current Limiter, Cutaway ViewB-10NIA20 Harness and Cable Interconnection DiagramB-20B-11DC Power CableB-12Vane Switch CableB-13DC Voltage Monitor Cable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |      |                                           |

| B-4NIA20 De-skew Timing. External Sync (CHT0 H)B-12B-5NIA20 De-skew Timing. EBUS CLK L and<br>MTR MBOX CLKB-13B-6H7420 Power SupplyB-14B-7NIA20 Card Cage ViewsB-15B-8NIA20 Card Cage in KL10-RB-16B-9NIA20 Current Limiter, Cutaway ViewB-17B-10NIA20 Harness and Cable Interconnection DiagramB-20B-11DC Power CableB-21B-12Vane Switch CableB-22B-13DC Voltage Monitor CableB-24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |      |                                           |

| B-5NIA20 De-skew Timing. EBUS CLK L and<br>MTR MBOX CLK.B-6H7420 Power Supply.B-7NIA20 Card Cage Views.B-8NIA20 Card Cage in KL10-R.B-9NIA20 Current Limiter, Cutaway View.B-10NIA20 Harness and Cable Interconnection Diagram.B-11DC Power Cable.B-12Vane Switch Cable.B-13DC Voltage Monitor Cable.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |                                           |

| MTR MBOX CLKB-13B-6H7420 Power SupplyB-14B-7NIA20 Card Cage ViewsB-15B-8NIA20 Card Cage in KL10-RB-16B-9NIA20 Current Limiter, Cutaway ViewB-17B-10NIA20 Harness and Cable Interconnection DiagramB-20B-11DC Power CableB-21B-12Vane Switch CableB-22B-13DC Voltage Monitor CableB-24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |                                           |

| B-6H7420 Power Supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |                                           |

| B-7NIA20 Card Cage Views                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | B-6  |                                           |

| B-8NIA20 Card Cage in KL10-RB-16B-9NIA20 Current Limiter, Cutaway ViewB-17B-10NIA20 Harness and Cable Interconnection DiagramB-20B-11DC Power CableB-21B-12Vane Switch CableB-22B-13Vane Switch Harness InstallationB-23B-14DC Voltage Monitor CableB-24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |                                           |

| B-9NIA20 Current Limiter, Cutaway ViewB-17B-10NIA20 Harness and Cable Interconnection DiagramB-20B-11DC Power CableB-21B-12Vane Switch CableB-22B-13Vane Switch Harness InstallationB-23B-14DC Voltage Monitor CableB-24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |                                           |

| B-10NIA20 Harness and Cable Interconnection DiagramB-20B-11DC Power Cable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |      |                                           |

| B-11DC Power Cable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |      |                                           |

| B-12Vane Switch Cable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |      |                                           |

| B-13Vane Switch Harness InstallationB-23B-14DC Voltage Monitor CableB-24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |      |                                           |

| B-14 DC Voltage Monitor CableB-24                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | B-13 |                                           |

| ······································                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |      |                                           |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | B-15 |                                           |

This reference manual provides a technically oriented description of the Network Interconnect Adapter (NIA20). This description includes detail on implementation and installation, as well as functional and logic characteristics. The NIA20 is required by Digital Equipment Corporation field service, manufacturing, engineering, software, and operational personnel.

This manual contains a preface, five chapters, and two appendices as outlined in the Table of Contents.

.

.

CHAPTER 1 INTRODUCTION

The network interconnect (NI), a major element in the network architecture of Digital Equipment Corporation, uses a single coaxial cable to transmit serial datagrams between stations (or nodes). The form of the datagrams (also called frames or packets) is dictated in the Ethernet specification.

The NI is used as a local area network (LAN) to link information processing equipment within an area (limited to a building or complex of buildings) through reliable, high-speed communications channels. Extensive and complex configurations are possible using the NI as the primary interprocessor and processor to corporate communications server products.

The NI has several advantages over other interconnects. It is a multiple-access network, not a point-to-point link. This design allows wiring and then simply tapping into the cable wherever the computing power is needed. Nodes can be added or removed from a network during its operation. There is no centralized control. Also, a system failure connected to the NI should not affect communications among other systems on the NI.